梁晓峰 叶晖

摘 要:文章对零中频接收机的直流偏置的产生进行了介绍,然后提出一种静态校准与动态校准相结合的两级直流偏置校准技术,既能消除因设计或工艺偏差造成的固有的直流偏置,也能消除由于实时环境因素造成的直流偏置分量。在保证校准具有较高的精度的同时也具备较高的实时校准能力。

关键词:零中频接收机;直流偏置;静态校准;动态校准

中图分类号:TN851 文献标识码:A 文章编号:2096-4706(2019)10-0038-04

Abstract:In this article the causes of DC offset in ZIF receiver is introduced,then a two-step DC offset calibration technique combining static calibration with dynamic calibration is presented. This technique can not only eliminate inherent DC offset caused by mismatch of design or manufacture technology,but also eliminate DC offset caused by real time environment. It can offer either high accuracy or real time cancellation.

Keywords:zero IF receiver;DC offset;static calibration;dynamic calibration

0 引 言

传统的射频接收机解调方式是射频信号(RF)进入天线,通过下变频技术转换为中频(IF)信号,再将中频信号转换为同相(I)和正交(Q)两路相互正交的基带信号。在中频部分需要加入中频滤波器,使电路变得相对复杂、集成度相对较低、功耗和成本也比较高。

近年来,随着通信系统对成本、功耗、面积等的要求越来越高,零中频接收机的使用变得越来越广泛。零中频接收机技术是相对于传统的两次甚至多次变频的中频接收机技术而言的。零中频接收机只采用了一次变频,射频信号经天线、低噪声放大器、混频器,直接将射频信号下变频为基带信号,然后经过ADC转换为相互正交的数字I/Q信号,之后再进行信道滤波、解调解码等。零中频接收机具有体积小、成本低以及易于集成和扩展等特点,已成为在射频接收机中极具竞争力的一种,在无线通信领域中得到广泛的应用[1]。

尽管具有上述多种优点,零中频接收机还是存在I/Q不平衡、直流偏置等主要缺陷[2]。其中直流偏置会叠加在有用信号上通过整个接收通道,影响有用信号在低频处的能量,导致信噪比恶化,还有可能造成混频器后的放大器以及模数变换器ADC饱和,从而不能有效地放大有用信号,导致射频接收机的解调精度下降以及误码率的提高[3],甚至无法正确接收信号。因此,直流偏置的消除是零中频接收机设计的关键之一。

本文将从三个部分来介绍直流偏置校准技术。第一部分提出零中频接收机现存的直流偏置的几个主要来源。第二部分主要介绍本文提出的零中频接收机的直流偏置校准的设计方案。第三部分则分别介绍两级直流偏置校准的设计与实现。

1 直流偏置的产生和对策

直流偏置的产生主要有以下四个方面:

(1)由于设计、制造工艺等造成混频器输出端不对称导致的共模直流偏置,这种直流偏置存在于每个芯片中[4];

(2)由于本振端口、混频器端口和低噪声放大器端口的隔离度不够高,导致本振信号泄漏到接收机的输入端,造成自混频,从而产生了直流分量,该直流分量是零中频接收机存在直流偏置的主要原因;

(3)由于温度、从天线端引入的环境噪声等各种环境因素造成的直流偏置;

(4)接收/发射工作模式在快速切换期间造成的直流偏置跳变。

从直流偏置的性质来说,可以分为两类,一是基本不随时间变化的,与接收机模拟前端的增益以及本振频率的相关性较大,如上文(1)(2)点所述,称为静态直流偏置;二是可随时间变化的,如上文(3)(4)点所述,称为动态直流偏置。

传统的技术对于直流偏置的消除主要在模拟电路的部分实现,主要方法有二[5]:一是通过交流耦合(AC Coupling)的方式来消除直流偏置,比如模拟高通滤波器,但这对模拟电路的精度有很高的要求,而且会增加较多的芯片面积;二是利用接收中的等待时间(idle time)来测量直流偏置,并储存在电容中,正常接收时再减去直流偏置量。然而采用模拟电路的实现方式,校准的时间会比较长,虽然对于校准静态直流偏置可能影响不大,但对于动态直流偏置校准还是会有较大影响。

而现有的数字校准技术中,为了简化直流偏置检测和校准电路,均在数字基带或者数字滤波电路中对接收数据进行采样处理,从而获得直流偏置,并在数字通道中减去;但在实际芯片中,经混频器输出的直流是和有用信号叠加在一起输入到跨阻放大器TIA,再经模数转换器ADC转换为数字信号的,当直流偏置存在,且值比较大时,将直接限制跨阻放大器TIA和模数放大器ADC输入的有效信号幅度的上下限,即跨阻放大器TIA或者模数转换器ADC会因输入信号过大而饱和,产生非线性失真[6],从而限制了整个接收机的动态范围,这将直接影响到接收机的两个重要指标:灵敏度和最大输入电平,从而恶化整个接收机的性能;为了应对比较大的直流偏置,必须在设计时增加放大器和ADC的动态范围[7],这又将大大增加跨阻放大器TIA和模数转换器ADC的设计难度以及动态功耗,给整个设计工作带来不必要的麻烦。

为了解决上述零中频接收机存在的直流偏置问题,本文提出了一种用于零中频接收机的,既不会降低放大器和ADC动态范围,又具有较高实时性的直流偏置校准技术。

2 设计方案

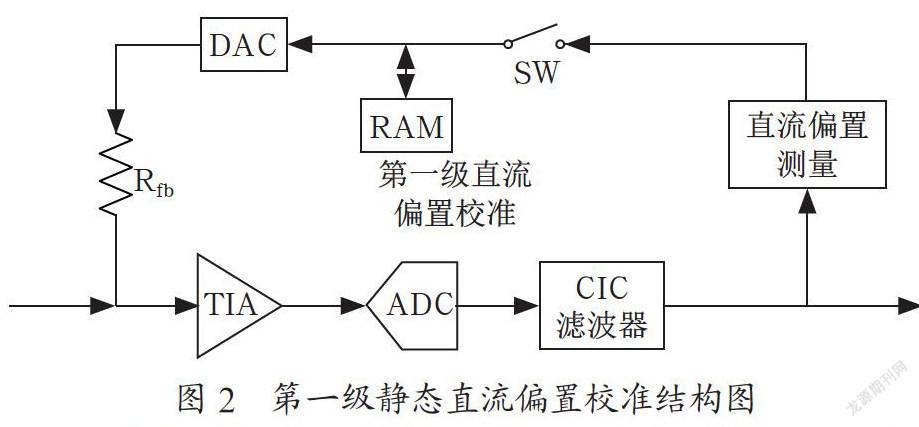

本文提出的直流偏置校准技术将分别针对静态直流偏置和动态直流偏置,采用了两级校准的结构。第一级直流偏置校准电路采用闭环结构,在天线端没有输入信号的条件下,获取芯片接收通道中的固有直流偏置,把获得的直流偏置值通过DAC反馈回放大器的输入端,可以消除混频器输出端所带的直流偏置。第二级直流偏置校准电路在第一级直流偏置校准电路校准后的基础上,在每次芯片进入接收模式后,且有用信号到达前,对ADC转换后的数字接收信号进行短时、迅速的直流偏置校准,把结果直接作用于数字接收信号,以消除由于实时环境因素造成的直流偏置分量。

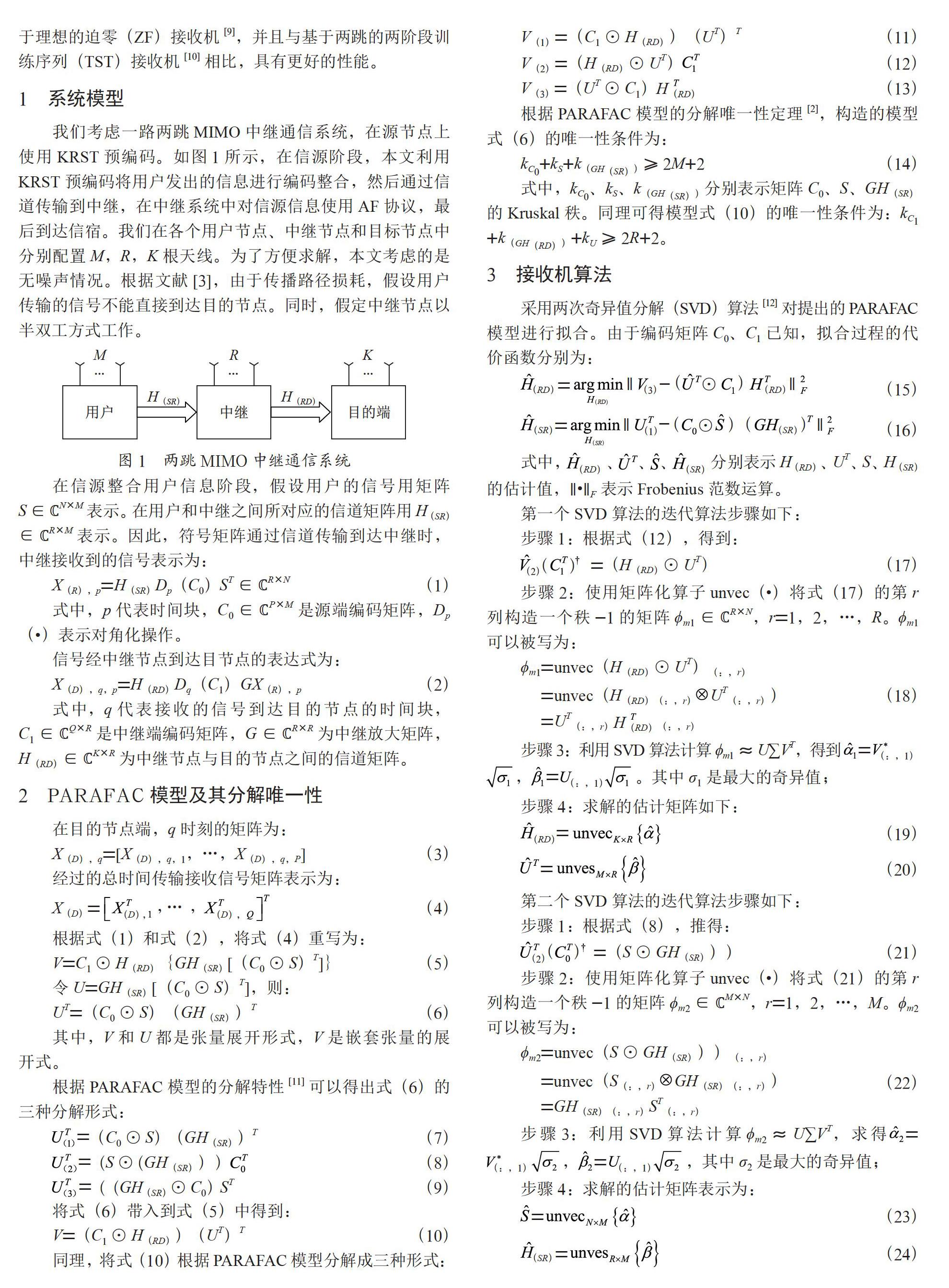

通过静态、动态两级直流偏置校准,则可达到校准芯片接收通道动态和静态直流偏置的目的,提高零中频接收机的接收性能。下面将详细描述两级直流偏置校准的实现方法,如图1所示。

2.1 第一级直流偏置校准

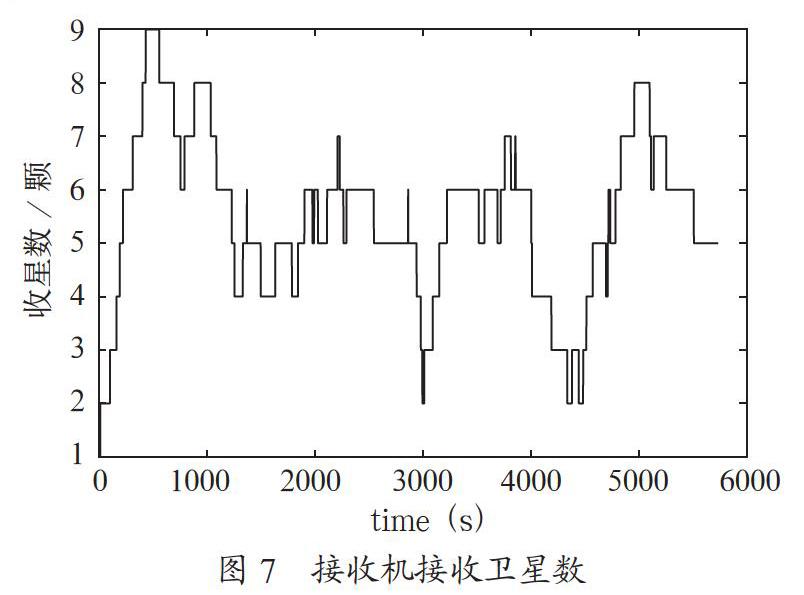

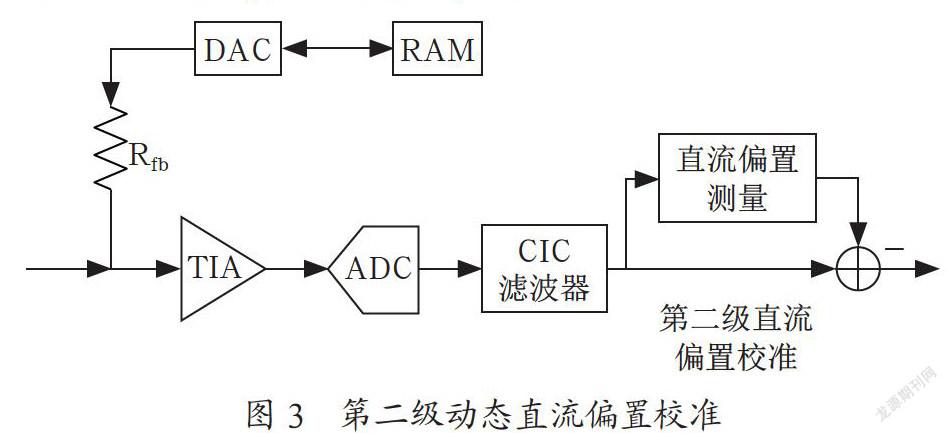

第一级直流偏置校准,即静态直流偏置校准,用于消除芯片接收通道中因设计或工艺偏差造成的固有的直流偏置。静态直流校准部分的电路结构如图2所示,核心部分由跨阻放大器TIA、模数转换器ADC、直流偏置测量模块、静态校准开关、RAM、数模转换器DAC和一个CIC滤波器组成。

在芯片上电时,设置射频天线开关为发射状态,由于天线开关的隔离作用,射频芯片接收端处于输入为零或十分接近零的状态,此时静态校准开关闭合,校准电路形成闭环负反馈回路,然后即可在初始化程序中启动第一级直流偏置校准,即启动静态直流校准。

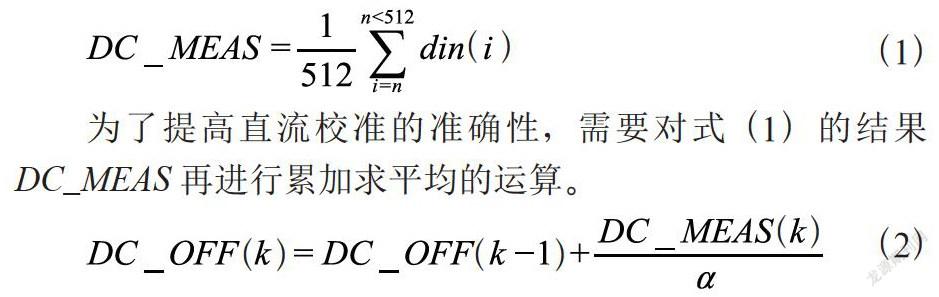

静态直流校准启动后,数字电路部分中的直流偏置测量模块对ADC转换后的数字信号进行较长时间的采样,每个测量结果均进行512次采样,然后进行累加和平均,完成后得到一个测量结果DC_MEAS。

为了提高直流校准的准确性,需要对式(1)的结果DC_MEAS再进行累加求平均的运算。

式(2)中k为重复测量的次数,α为再一次求平均的除数,正常来说,k的取值应等于α,重复次数等于求累加平均的次数,则等效于进行了k次累加,就对累加结果除k求平均,但为了保证测量过程的灵活性与可控性,避免对直流偏置的运算有所偏差,因此将芯片中k设计为一个可编程数值。

为了简化运算,降低电路的复杂性,α默认以2的n次幂取值,α选择这种取值形式的主要原因在于电路实现中只需对被除数进行向右移位运算即可,不需要进行复杂的除法运算。芯片中默认k和α间的取值关系参考如下。

当求得第k次的运算结果后,所得的DC_OFF(k)即为静态校准的最终结果,该结果将保存于芯片内部的RAM中,同时静态校准开关将断开,至此静态直流校准结束。

正常工作模式下,进入接收状态后,芯片将根据当前设置的模拟增益档位和本振频率分段在对应的RAM地址中取出静态校准所得的直流偏置值,并将此直流偏置值经数模转换器DAC转换为模拟信号反馈到跨阻放大器TIA的输入端。在TIA和ADC之前就消除掉由于芯片主要电路参数变化(模拟增益变化、本振频率变化)而产生的直流偏置分量以及芯片个体因生产工艺偏差所固有的直流偏置分量,同时补偿了TIA和ADC自身对直流偏置的影响,有效地防止了TIA和ADC因为较大直流偏置而饱和产生的非线性失真。

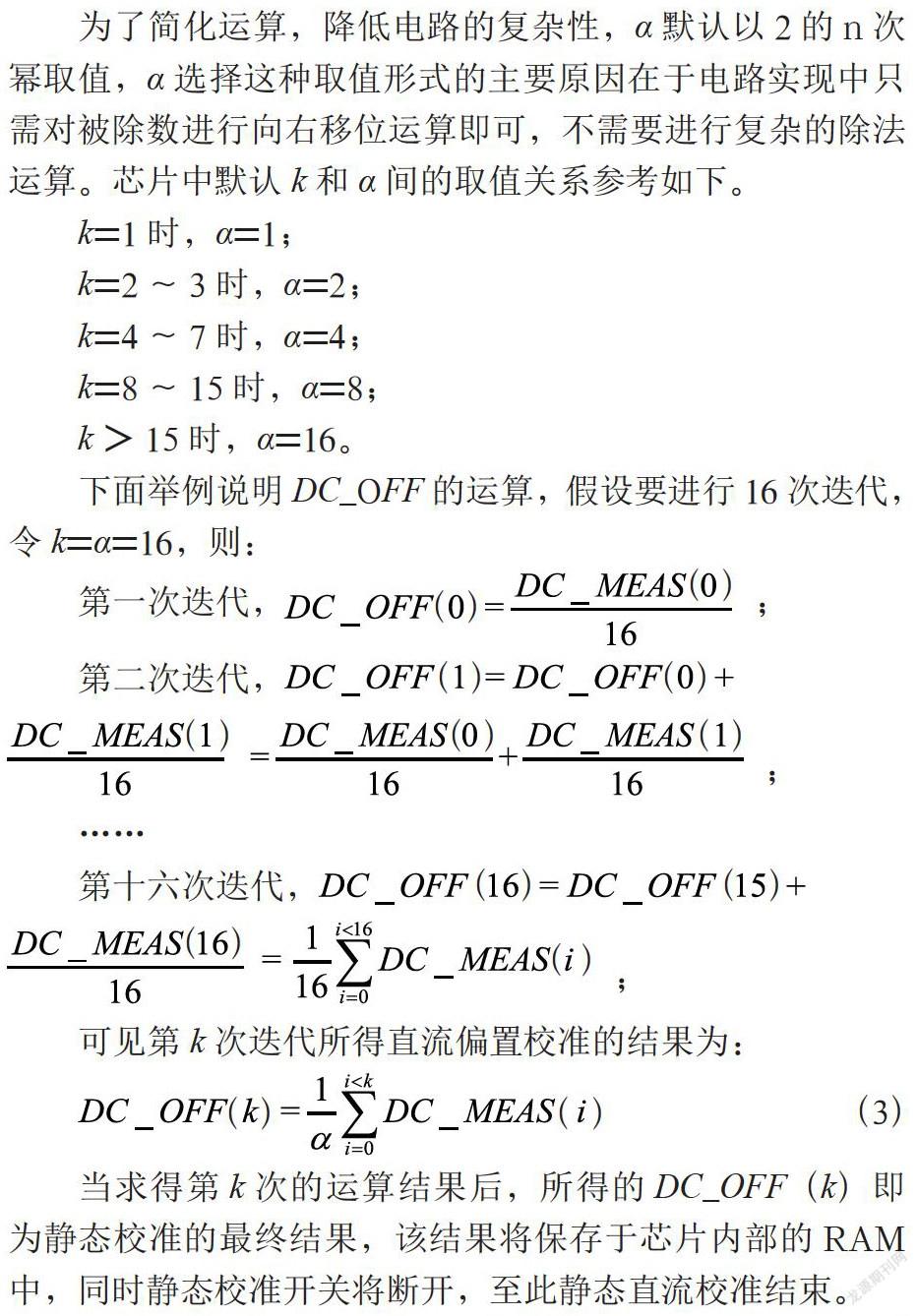

此外,考虑到针对不同的本振频率以及模拟增益,接收通道中固有的直流偏置会有所不同。因此设计中将芯片的本振频率分段,校准过程会在不同的本振频率分段中进行,再根据不同档位的低噪声放大器LNA增益各进行一次直流偏置运算,求得对应的直流偏置值。假设芯片的本振频率需要覆盖100MHz的范围,则在设计时将本振频率划分为5个频率分段(每20MHz一个分段),并将LNA模拟增益分为高低两档,依次进行上述第一级静态直流偏置校准,则总共进行了10次直流偏移校准,将得到与频率分段和增益档位对应的20个直流偏置校准结果,存储方式如表1所示。

如表1举例的本振频率范围和模拟增益档位所示,一共进行了10次静态直流校准,因此完成整个校准过程需要较长的时间,考虑到静态直流偏置固有地存在于接收机通道中,基本不随时间变化,因此第一级直流偏置校准安排在对时间较不敏感的芯片上电初始化时进行,在整个芯片上电工作过程中只运行一次。

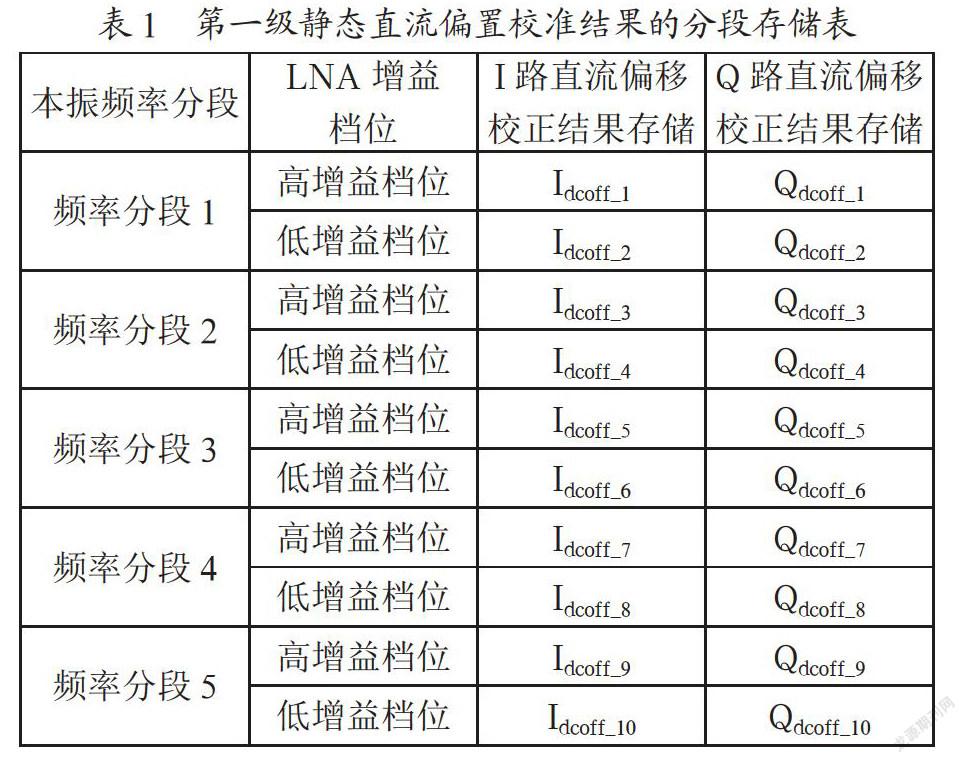

2.2 第二级直流偏置校准

第二级直流偏置校准,即动态直流偏置校准,是在第一级直流偏置校准的基础上进行进一步的校准。如图3所示,在进行第二级直流偏置校准时,第一级直流偏置校准的结果将从对应的RAM地址中读出,并作用于反馈路径的数模转换器DAC上,反馈给跨阻放大器TIA的输入端,消除静态直流偏置。经第一级直流偏置校准后,残留的直流分量相对于校准前已经大大减小,但考虑到芯片面积与功耗等因素,导致模数转换器DAC的位数不能太高,其实现精度也会对第一级直流偏置校准的结果产生影响,因此会有少量残余的静态直流分量未能消除。该残余直流将通过模数转换器ADC进入到数字前端中,并将在第二级直流偏置校准过程中与动态直流偏置一并得以消除。

由于环境因素是不断变化的,因此动态直流偏置也是随时间变化的,需要实时进行校准。第二级动态直流偏置校准必须在接收机正常工作时实施才能有效消除当时的动态直流偏置。然而校准过程中,接收通道中的有用信号会给校准引入较大的测量误差。因此动态直流偏置校准需要在接收机通道刚进入接收状态而有效数据还未到达时进行,此时做动态校准最能体现当前电路中如温度、从天线端引入的环境噪声干扰等因素对直流偏置的影响。

进入接收模式后,芯片内部的模拟电路需要一定的稳定时间才能进入正常工作状态,之后接收到的有用信号也需一定的通道延时才能进入直流偏置测量模块,期间有用信号需经过低噪声放大器LNA、混频器MIXER、跨阻放大器TIA、模数转换器ADC以及积分梳状滤波器CIC。因此动态直流校准的耗时不能超过稳定时间与通道延迟之和。动态直流校准采用的算法与静态直流校准类似,但采用更少的累计次数,以求在更短的时间内完成校准。例如对DC_MEAS的计算,静态直流校准采用了512次采样进行累加求平均,而动态直流校准则只用8次采样进行累加求平均,校准时间将大大缩短。动态直流校准的结果将直接在数字信号处理模块内从I/Q通道的有效数字信号中减去,校准的结果不需要保存在芯片中,而是在每次进入接收模式时都进行一次校准,以达到实时校准的目的。

对于DC_OFF的计算还是采用式(3)的形式,对第二级直流偏置校准的结果DC_MEAS做累加求平均运算,以获得更高的校准精度。

如上述可见,动态校准和静态校准在数字信号处理中的直流偏置测量算法上是相同的,只是根据测量时间长短的需求不同,所采取的累加长度有所不同。两级直流校准并不会在同一时间启动,因此可以共用直流偏置测量模块,以达到节省芯片资源的目的,只要在实际应用时通过寄存器来配置校准长度即可。

2.3 仿真结果

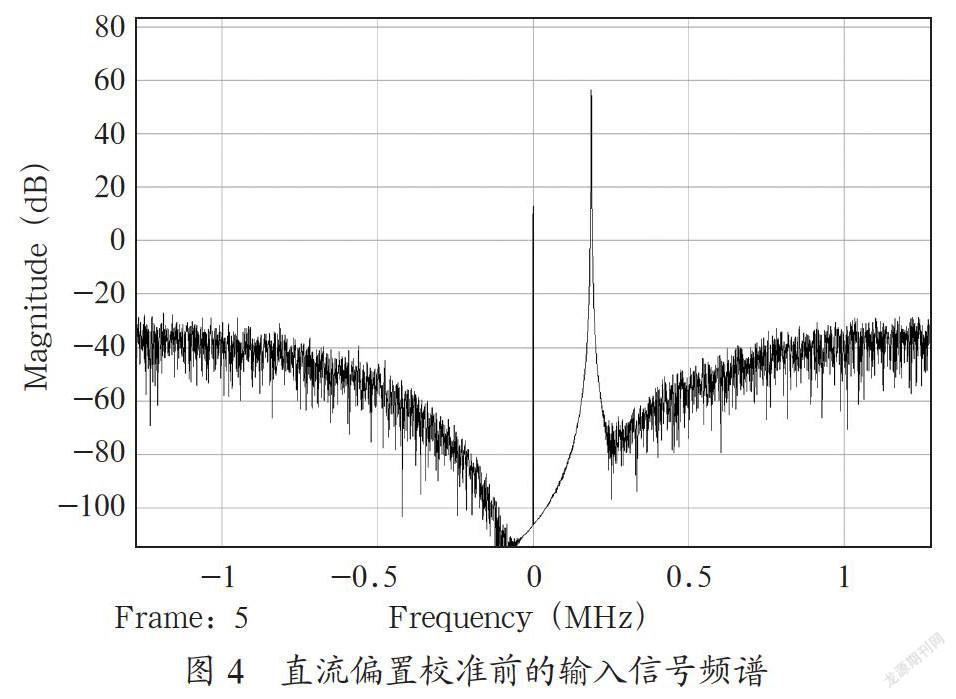

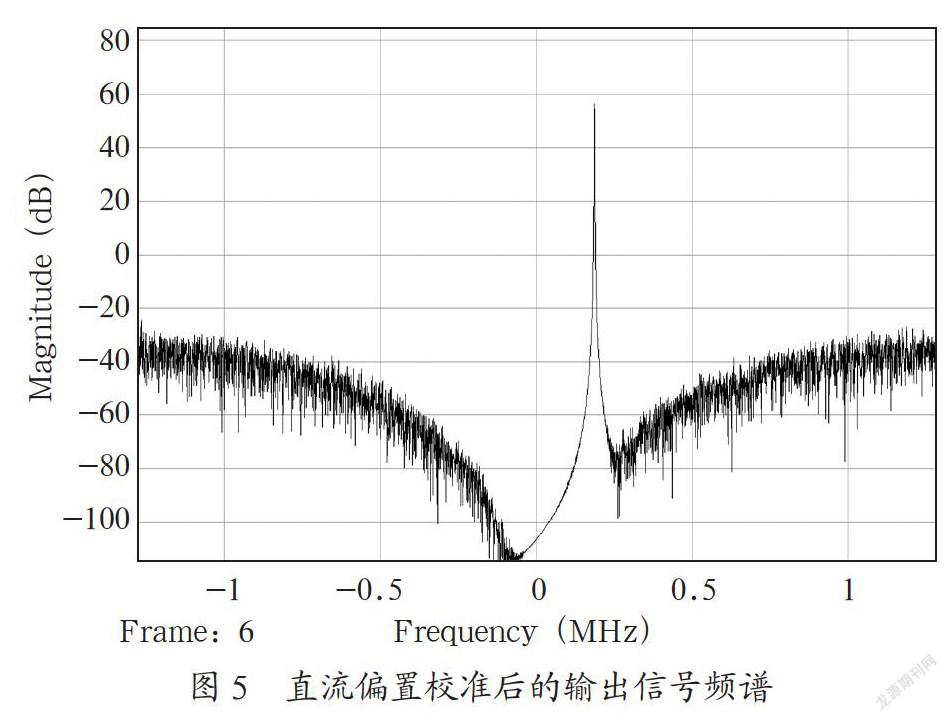

图4、图5分别为两级直流偏置校准技术使用前后的仿真结果,当输入信号幅值设置为0.7(假设信号满摆幅时幅值为1),I/Q两路信号直流偏移分别取0.002和-0.004时,直流偏置校准前接收信号的频谱如图4,从频谱中可见输入信号中带有较大的直流分量。经本文提出的两级直流偏置校准后的信号频谱如图5所示,可见接收信号中的直流偏置已经被很好地消除了,可见本文提出的校准技术是确实可行且有效的。

3 结 论

针对零中频接收机存在的直流偏置问题,本文提出了一种动态和静态结合的直流偏置校准技术,既能消除因设计或工艺偏差造成的固有的直流偏置,也能消除由于实时环境因素造成的直流偏置分量。在保证了校准具有较高的精度的同时也具备较强的实时校准能力。

参考文献:

[1] 李智群,王志功.零中频射频接收机技术 [J].电子产品世界,2004(13):69-72.

[2] 王自强,张春,王志华.无线接收机结构设计 [J].微电子学,2004(4):455-459.

[3] Abidi AA. Direct-conversion radio transceivers for digital communications [J]. Solid-State Circuits,IEEE Journal of,1995,3(12):1399-1410.

[4] Yoshida H,Tsurumi H,SUZUKI Y. DC offset canceller in a direct conversion receiver for QPSK signal reception [C]//Personal,Indoor and Mobile Radio Communications,1998. The Ninth IEEE International Symposium on. S.l.:s.n.,1998:1314-1318.

[5] 范俊,李永明.解决零中频架构直流漂移的自校正方案 [J].微电子学,2005(2):114-117.

[6] Elahi I,Muhammad K. IIP2 calibration by injecting dc offset at the mixer in a wireless receiver [J]. IEEE Transactions on Circuits and Systems II:Express Briefs,2007,54(12):1135-1139.

[7] Horlin F,Bourdoux A. Digital Compensation for Analog Front-Ends:A New Approach to Wireless Transceiver Design [M]. S.l.:s.n.,2008.

作者简介:梁晓峰(1982-),男,汉族,广东广州人,数字IC设计工程师,电子技术工程师,硕士研究生,研究方向:射频、数字集成电路;叶晖(1976-),男,汉族,湖南湘阴人,数字IC设计工程师,电子技术工程师,博士研究生,研究方向:射频、数字集成电路。