摘" 要:首先文章介绍了目前实现理想二极管技术方案优缺点,对方案进行改进,设计一种超低损耗理想二极管控制电路,电路由PMOS主管、PMOS辅管、两个偏置电阻组成。优先选用相同参数、封装在一起的集成PMOS辅管和两个偏置电阻组成比较电路,控制PMOS主管的导通与截止,当输入电压VCC不小于输出电压Vout时,PMOS主管导通;反之PMOS主管截止,防止Vout电流倒灌至VCC,保护VCC电源前级电路。本设计的优势在于电路具有防止倒灌功能,可以保护前级电路;整个电路具有非常低静态电流损耗;组合逻辑比较电路简单,成本较低,实用性强。

关键词:超低损耗;理想二极管;PMOS辅管;倒灌电流

中图分类号:TN710 文献标识码:A 文章编号:2096-4706(2024)24-0007-06

Design of an Ultra-low Loss Ideal Diode

CHEN Shiping1, LI Shuohan1, FAN Feifei1, CHEN Jinjie2, FENG Junjie1

(1.Guangdong Polytechnic of Science and Trade, Guangzhou" 511500, China; 2.Hunan City University, Yiyang" 413000, China)

Abstract: Firstly, this paper introduces the advantages and disadvantages of current technology scheme for realizing ideal diode, and it improves the scheme to design an ultra-low loss ideal diode control circuit, which consists of a PMOS main transistor, a PMOS auxiliary transistor, and two bias resistors. It is preferable to use an integrated PMOS auxiliary transistor with the same parameters and packaged together along with two bias resistors to form a comparison circuit, which controls the conduction and cutoff of the PMOS main transistor. When the input voltage VCC is not less than the output voltage Vout, the PMOS main transistor conducts. On the contrary, the PMOS supervisor cuts off to prevent Vout current from flowing back into the VCC and protect the front-end circuit of the VCC power supply. The advantage of this design is that the circuit has the function of preventing backflow, which can protect the front-end circuit. The entire circuit has very low static current loss. The combination logic comparison circuit is simple, low-cost, and highly practical.

Keywords: ultra-low loss; ideal diode; PMOS auxiliary transistor; reverse current

0" 引" 言

二极管具有天然单向导通特性[1],具有防止倒灌功能,得到越来越多的应用,特别是肖特基二极管具有较小导通压降,正受到越来越多设计师的欢迎。相同导通电流条件下,肖特基二极管的导通压降大于MOS管导通压降,对于一些压降敏感的电路来说,更倾向于使用具有低阻抗特性的MOS管,以降低静态损耗。现在有很多电源自带防止倒灌的功能,如外部设备连接到计算机的USB端口时,设备绝对不能将电流反向流入计算机接口,否则会烧坏计算机。目前Oring电路应用于很多场合,保证各电源互相独立、无倒灌现象,常应用于均流电路中,满足不同功率需求。因此需要一种超低静态损耗[2-3]的理想二极管(ideal diode),进一步降低导通压降,并具有防倒灌和保护前级电路功能[4-5],使损耗降到最低,提高电源利用率。

1" 技术方案对比

理想二极管是一种理想的单向导通(One-Way Conduction Device)装置,工作原理可以简单描述为:当施加正向电压时,理想二极管导通;当施加反向电压时,理想二极管截止。当然这在现实物理世界中是不存在的。理想二极管工作原理基于假设模型,实际的二极管会受到一些非理想因素的影响,如正向导通压降和反向漏电流。这些非理想因素会导致实际二极管的特性和理想二极管存在不同。但是,理想二极管模型在简化和分析电路中仍然具有重要的作用,可用于描述二极管的基本工作原理和近似特性,理想二极管模型仍然是理解和分析二极管工作的基础。

理想二极管需具有以下三种特性:

1)正向导通(正向偏置),当电源正极施加在二极管的P极(阳极)上,且电压超过二极管的正向导通阈值时,二极管完全导通,电流可以通过,导通压降(正向压降)为零,等效电阻为0,相当于短路。

2)反向截止(反向偏置),当反向电压施加在二极管的N极(阴极)上,二极管处于截止状态,理想二极管的反向电流IR为零,等效阻抗为无穷大,相当于断开(开路)。

3)零漏电流,正向导通状态下,二极管的正向电流可以很大;反向截止状态下,二极管的反向漏电流为零。

现有技术实现方案在低损耗方面存在一定的不足:

1)二极管方案[5]:二极管本身具有单向导电性,是天然的Oring电路,最基本的Oring电路就是在输出端加一个二极管。使用二极管串接在电源上,电路简单,其缺陷是二极管大约有0.6~0.7 V的导通压降,导通压降会随着输入电流成比例的功率损耗。随着电流增大,导通压降也会变大,如用肖特基二极管取代二极管可以降低导通压降,但损耗还是比较大:以某公司生产肖特基二极管SS54为例,电流0.1 A、1 A、10 A、20 A对应的导通压降分别为0.3 V、0.4 V、0.85 V、1.4 V,对应的导通损耗分别为0.03 W、0.4 W、8.5 W、28 W,意味着导通电流越大,损耗也越大。肖特基二极管导通压降,换算为电流损耗,其静态电流损耗至少为毫安级。

2)MCU+PMOS主管方案[6]:电路需要一个额外的偏置电源VBIAS、微控制器(MCU),使用MCU的两路ADC对PMOS主管的漏极(D极)和源极(S极)进行电压采集并比较两者的电压大小,进而控制PMOS主管的导通与截止,不足之处工作电流损耗至少为毫安级,电流损耗较大,且需要使用额外的偏置电源VBIAS和MCU,方案成本高。

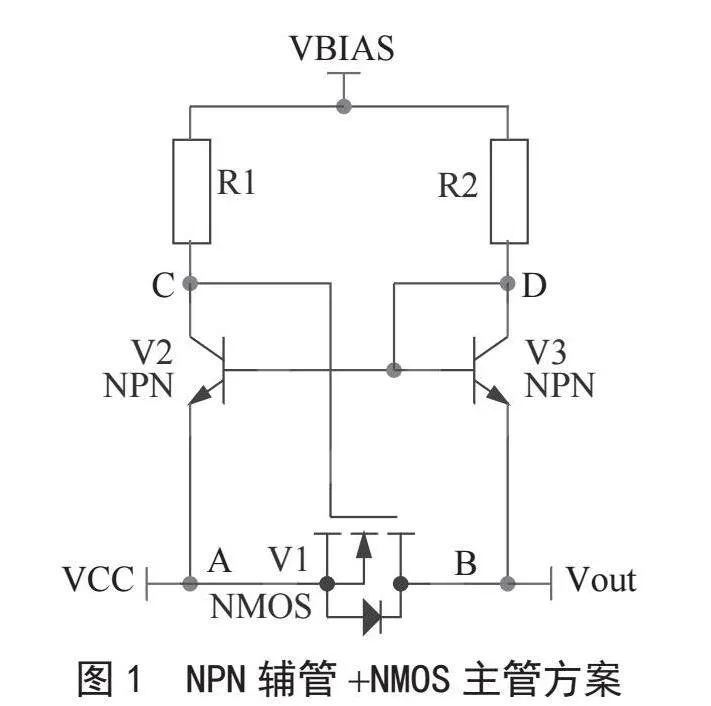

3)NPN辅管+NMOS主管方案:如图1所示,电路需要一个额外的偏置电源VBIAS>VCC+VTN(VTN为NMOS管导通阈值电压),使用相同厂家同一批次的NPN辅管,保证两个管子参数基本一致,或者优选封装在一起的NPN辅管,这样就几乎相等了,从而可以保证NMOS主管的开关和防倒灌功能,不足之处NPN辅管的偏置电阻为千欧姆级,静态电流损耗至少为毫安级,电流损耗较大,且需要使用额外的偏置电源VBIAS。

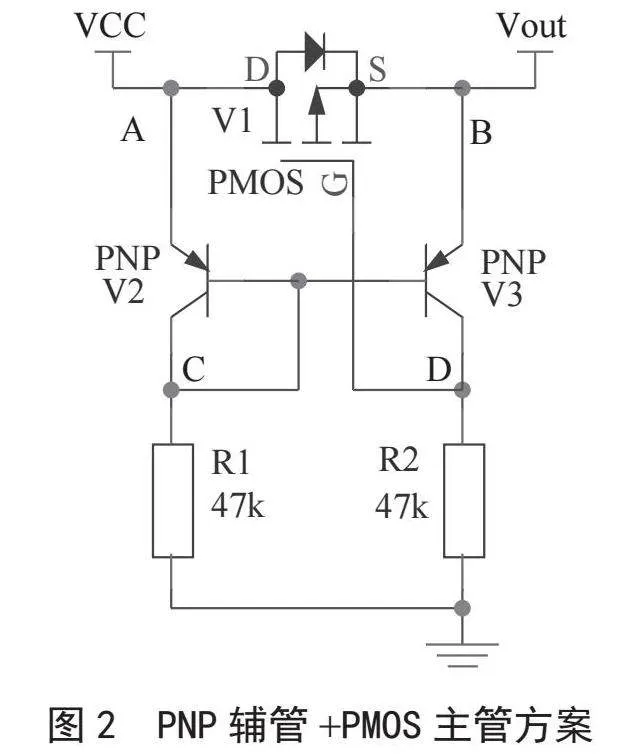

4)PNP辅管+PMOS主管方案:如图2所示,选用封装在一起的两个PNP辅管,可以保证两个PNP辅管参数基本一致,从而可以保证恰当的开关和防倒灌功能,不足之处PNP辅管的偏置电阻同样为千欧姆级,静态工作电流损耗至少为毫安级,电流损耗较大。

5)理想二极管方案:如使用凌特公司[7](Linear Technology)推出双通道理想二极管LTC4413,它特别针对减少热量、压降与占板面积及延长电池使用时间而设计,非常适用于需要理想二极管“或”功能来实现负载共享或两个输入电源间自动切换的应用。LTC4413在500 mA和2 A时分别具有80 mV和210 mV的导通压降,泄漏电流为1 μA,较分立二极管“或”解决方案有极大改进。LTC4413内置两个100 mΩ的PMOS主管,每个PMOS主管的最大正向电流限制在恒定2.6 A,内部热限制电路在出现故障时可保护器件。不足之处:输出电流仅为1 A,静态电流约为40 μA,且存在1 μA左右的反向倒灌电流将从输出端OUT流向输入端IN;9 μA漏极开路STAT引脚指示所选通道的导通状态,并可用于驱动外部PMOS主管以控制第三个备用电源;LTC4413价格高昂,国内某元器件商城,100片批量购买,单价超过45元。

2" 电路设计

按照控制电源极性分,分为High Side(高端、高侧、高边)理想二极管、Low Side(低端、低侧、低边)理想二极管,分别类似于控制市电220 V的火线、零线。高端理想二极管:它通过外部使能信号的控制来连接或断开电源(电池或适配器)至特定的负载。相比低端理想二极管,高端理想二极管“流出”电流至负载,而低端理想二极管则将负载连接或者断开负极,因此它从负载“汲入”电流。

理想二极管等效电路分为电子开关和驱动装置两部分。

驱动装置(又称为驱动电路、电压比较器、逻辑控制电路、控制器)一般采用电压比较器或运算放大电路等,用于检测电子开关P极、N极两端的电位差。当阳极(P极)电位高于阴极(N极)电位时,驱动装置输出驱动信号至电子开关的控制端使电子开关导通,电子开关导通后,电流即可由P极经电子开关通道流向N极;反之,若P极电位低于N极电位,驱动装置输出使电子开关截止所需的驱动信号,故P极与N极间处于断路(截止)状态,电子开关处于关闭状态。驱动装置一般具有低工作静态电流、超低关断电流、稳压正向电压和快速反向电流响应等重要特性,因此能够在各种应用中实现理想二极管。

实现电子开关功能的电子元器件主要有MOS管:MOS管工作在可变电阻区时:MOS管漏源沟道电阻基本上仅受漏极、源极电压VGS控制。当VGS一定时,漏源导通电流ID与VDS呈线性关系,该区域近似为一组直线,MOS管漏极、源极间相当于一个受VGS控制的可变电阻。夹断区(等效于截止区):漏源沟道被全部夹断ID = 0,MOS管不工作。同样,可变电阻区和夹断区用于开关电路,包括信号开关、电源开关等电路。

MOS管因工艺提升,自身性质等因素,其导通内阻较小,功率型MOS管很多是毫欧姆级,甚至更小,具有很强的电流导通能力,导通压降小,损耗特别小,小电流时导通压降非常小,几乎可以忽略不计,因此选用MOS管作为理想二极管的主管是一种比较理想的选择。现在的MOS管导通阻抗可以做到几毫欧姆,假设导通阻抗为10 mΩ,导通电流为1 A,通过MOS管导通压降仅有10 mV,压降非常小,可以忽略不计。

MOS管开关等效电路特点,MOS管截止时,MOS管漏源极断开阻抗RDS(OFF)非常大;MOS管导通时,MOS管漏极、源极之间可以等效为一个电阻,导通阻抗RDS(ON)比较小,大约是mΩ数量级(信号型MOS管为欧姆数量级、功率型MOS管可低至毫欧姆级,与VGS有关),与VGS大小有关,导通状态下的电阻一般不能忽略不计。若VGS>>VTN,RDS(ON)近似与VGS成反比,VGS越大导通电阻越小,ID近似与V2GS成正比,ID与VGS关系的曲线称为MOS管的转移特性曲线。

PMOS型高端理想二极管,选用PMOS管作为主管,由于漏极与电源VCC相连,电源VCC通过体二极管至源极进行自我偏置,栅极电压低于源极电压很容易实现,不需要特定的内部升压电路或外部高电压,就可以实现PMOS主管导通与截止。PMOS型高端理想二极管在要求设计复杂度不高的低功率系统或者要求将电源电压(正极)传递给负载的输入电压系统中具有一定优势。

针对上述方案进行改进,设计一种超低损耗的理想二极管,进一步降低导通压降,并具有防倒灌,保护前级功能,使损耗降到最低,提高电源利用率。

低功耗高端理想二极管采用PMOS管为主管、PMOS辅管组成的高端理想二极管[8-10],PMOS主管导通压降比较小,可以应用于中等电流场合,一般功率PMOS主管的导通电流可以达几安培。

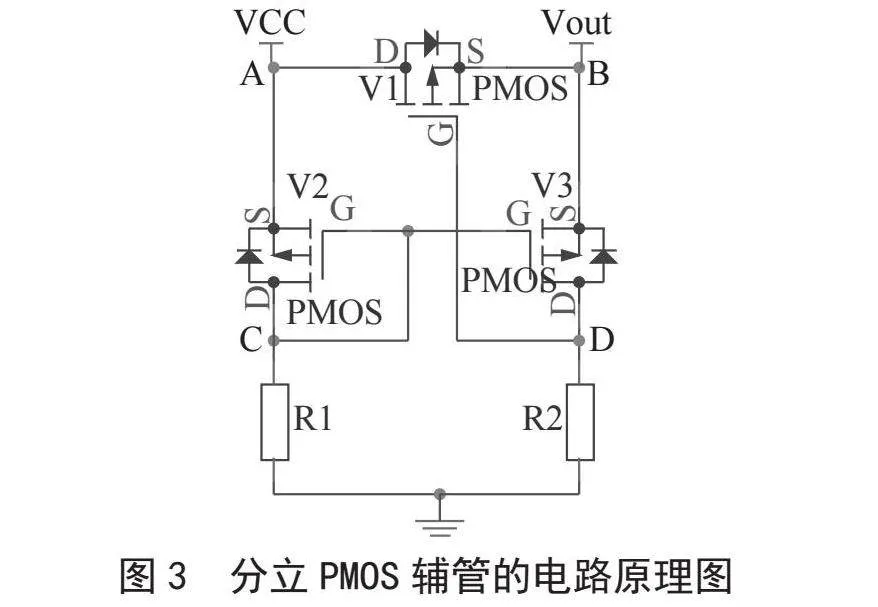

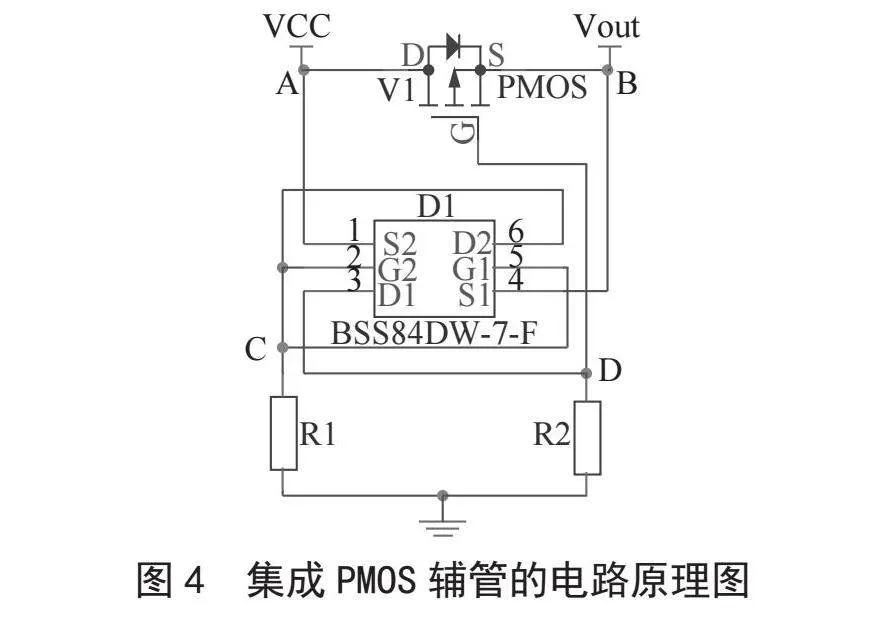

电路包括PMOS主管(V1),采用分立的两个PMOS辅管(V2、V3,如图3所示)或者集成的PMOS辅管(D1,如图4所示)、两个偏置电阻(R1、R2)组成。具有相同的参数、封装在一起的PMOS辅管和串接两个偏置电阻组成比较电路控制PMOS主管V1的导通与截止:当输入电压VCC不小于输出电压Vout时,PMOS主管V1导通;反之PMOS主管V1截止,防止Vout电流进行倒灌至VCC,保护VCC电源前级电路。由于MOS管属于电压器件,MOS管导通和截止时其电流非常小,串接大阻值电阻,偏置电流可以忽略不计,导通时只损耗很小的电流(小于微安级),与传统肖特基二极管或PNP辅管控制的PMOS主管电路相比,损耗降低很大,PMOS辅管组成的电路属于超低损耗控制器,理想二极管电路电流损耗低于微安级。

根据不同损耗要求选用漏极与源极之间的导通电阻合适的PMOS主管,满足损耗需求。对于大功率的电源控制,PMOS主管可以选择漏极与源极之间的导通电阻为数毫欧、通过电流大的功率管器件,比较电路由PMOS辅管和电阻组成,通对PMOS主管的漏极和源极之间的电压采样、比较后,输出不同的电平控制PMOS主管的导通与截止,由于MOS管属于电压器件,MOS管导通和截止时其电流非常小。选用漏极与源极之间的导通电阻为数毫欧的PMOS主管,可以通过很大电流(百安培级),通过PMOS主管的导通压降很小,可以近似为一个理想二极管。

3" 仿真测试

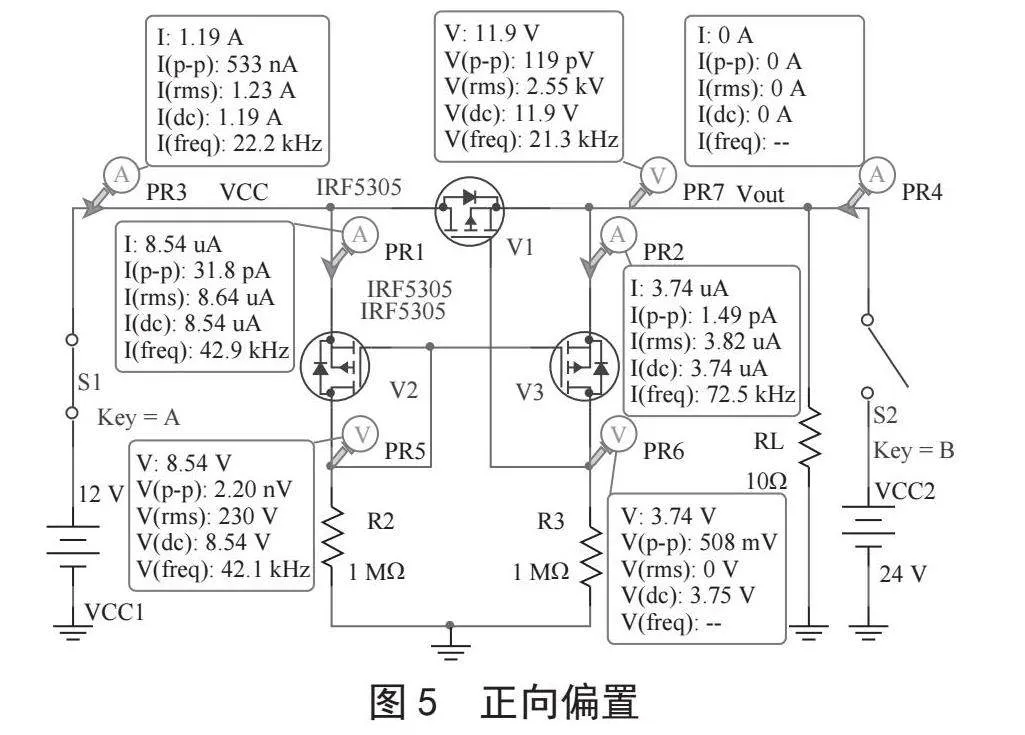

测试过程以分立的PMOS辅管为例[11],V1管、V2管、V3管使用International Rectifier公司的IRF5305:导通阈值电压最小值VTP(MIN)= -2.0 V、最大值VTP(MAX)= -4.0 V,未给出典型值VTP,导通电流为31 A/55 V,导通阻抗RDS(ON)= 0.06 Ω(VGS = -10 V),具体仿真如下:

当VCC无电源时,PMOS辅管(V2、V3)的栅极被电阻R1下拉至负极,V2管的栅极电压为0 V,PMOS辅管(V2、V3)截止,Vout无任何输出。

正向偏置:当VCC接上电源时(VCC1=12 V),负载RL = 10 Ω,如图5所示,对V2管而言,V2管栅极、漏极短接在一起,即V2G = V2D = V3G = 8.54 V,V2GS = V2DS = V2D-V2S = 8.54 V-12 V = -3.46 V<VTP,V2管导通,导通电流为8.54 μA(检测点PR1);V3GS = 8.54 V-11.9 V = -3.36 V<VTP,V3管导通,导通电流为3.74 μA(检测点PR2),即V3管漏源通道阻抗大于V2管漏源通道阻抗,即R3DS(ON)>R2DS(ON)。V1GS = 3.74 V-11.9 V = -8.16 V<VTP(MAX),V1管正向导通,导通电流1.19 A,V1管的导通压降为12 V-11.9 V = 0.1 V(对应导通阻抗RDS(ON)= 0.1 V/1.19 A = 0.084 Ω)。

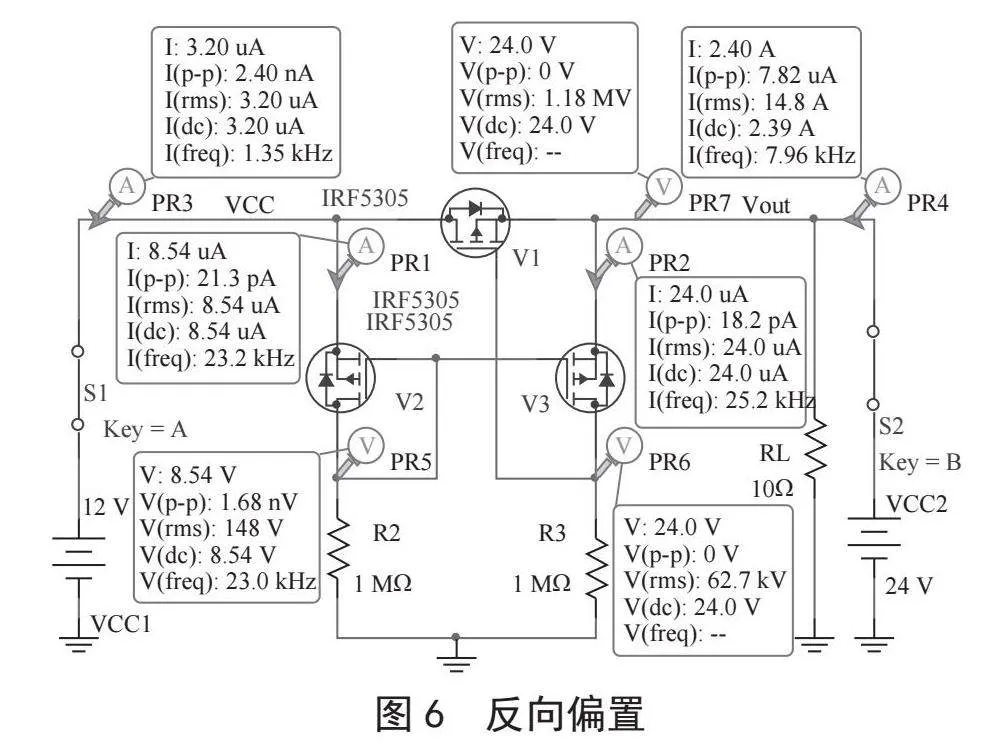

反向偏置:VCC1 = 12 V,VCC2 = 24 V(开关S1、S2闭合),V2GS = V2DS = V2D-V2S = 8.54 V-12 V = -3.46 V<VTP,V2管导通,导通电流为8.54 μA(检测点PR1);V3GS = 8.54 V-24 V = -15.46 V<VTP(MAX),V3管导通,导通电流为24.0 μA(检测点PR2),即V3管漏源通道阻抗低于V2管漏源通道阻抗,即R3DS(ON)<R2DS(ON)。V1GS = 24 V-24 V = 0 V>VTP(MIN),V1管反向截止,无反向电流,VCC1输出偏置电流为3.20 μA,电路可以实现防倒灌功能,保护输入电源前级电路。反向偏置图如图6所示。

4" 性能测试

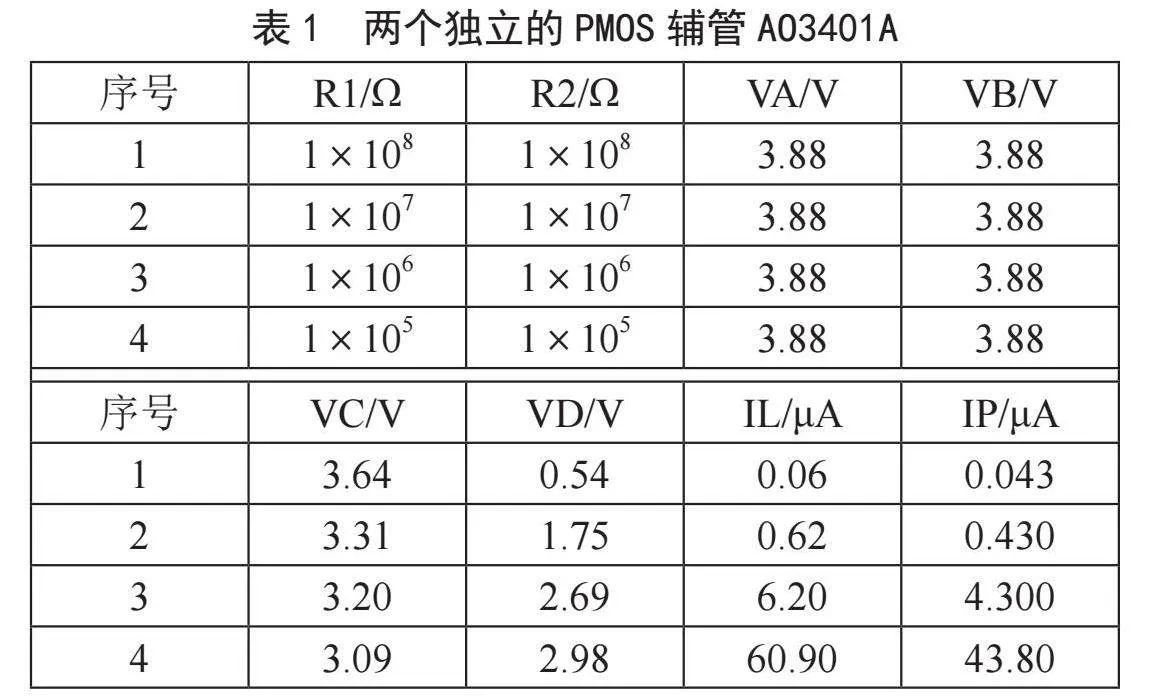

根据图3、图4原理图设计PCB板进行测试,PMOS主管使用AO3401A,比较电路部分的两个辅管分别采用两个独立的PMOS辅管AO3401A、集成PMOS辅管BSS84DW-7-F,焊接、装配后测试。PMOS辅管采用两个分立元器件AO3401A,AO3401A管导通阈值电压典型值VTP = -0.9 V(VTP(MIN)= -0.5 V、VTP(MAX)= -1.3 V),测试结果如表1第二行所示:使用3.88 V锂电池供电时(偏置电阻均为10 MΩ),VCC = VA = 3.88 V、Vout = VB = 3.87 V、VC = 3.28 V、VD = 1.73 V。

1)当VCC接上电源时(3.88 V),由图3可知PMOS辅管V2的栅极和漏极短接,V2G = V2D = VC,V2GS = V2DS,所以V2GS = VC-VA = 3.28 V-3.88 V = -0.60 V<VTP(MIN) = -0.5 V,V2管导通,导通电流小于VA/R1 = 3.88 V/10 MΩ = 0.388 µA。V3GS = VC-VB = 3.28 V-3.87 V = -0.59 V<VTP(MIN) = -0.5 V,V3管弱导通,即V3管漏源通道阻抗大于V2管漏源通道阻抗,即R3DS(ON)>R2DS(ON)。刚开始V1管利用自身的体二极管导通,Vout≈VCC-0.6 V,V1GS = VD-VB =" 1.73 V-VCC+0.6 V = -1.55 V<VTP(MAX) = -1.3 V,V1管漏源通道导通,不再经过PMOS辅管V1的体二极管高阻抗通道,Vout≈VCC。

从原理上来讲,V2管由于漏极和栅极相连,漏极和栅极电压相等,即V2D = V2G、V2DS = V2GS,对于PMOS管而言有VDS<VGS-VTP,对于NMOS管而言有VDS>VGS-VTP,就是说正常情况下它工作在饱和(放大/恒流)区的,这种结构表现了与两端电阻相似的小信号特性,等效阻抗为1/gm。

2)当VCC有电时,且Vout>VCC时,PMOS辅管(V2、V3)的栅极被电阻R1下拉至负极,PMOS辅管V2导通、V3导通。VCC = VA = 3.88 V,VB( = Vout)接上4.36 V电源后,VC = 3.28 V、VD = 4.36 V,V2DS = V2GS = V2D-V2S = 3.28 V-3.88 V = -0.6 V<VTP(MIN)、V2管导通;V3GS = VC-Vout = 3.28 V-4.36 V = -1.08 V<VTP(MIN),V3管导通,即V3管漏源通道阻抗小于V2管漏源通道阻抗,即R3DS(ON)<R2DS(ON);V1GS = V1G-V1S = VD-VB = 0V,V1管截止,VCC输出静态电流IL为0.3 μA(无倒灌电流流入VCC)、VB(接上4.36 V电源)静态输出电流IP为0.43 μA。

两个偏置电阻分别焊接为100 MΩ,1 MΩ、100 kΩ,测试的结果分别如表1第一、三、四行所示,比较电路能够有效控制PMOS主管导通与截止,接负载后可以通过数安培电流,即能够通过大电流和具有防倒灌功能,大大扩展了应用范围。

集成PMOS辅管采用BSS84DW-7-F,测试电路如图4所示,PMOS辅管导通阈值电压典型值VTP=-1.6 V(VTP(MIN)=-0.8 V、VTP(MAX)=-2.0 V),使用3.88 V锂电池供电时(偏置电阻均为10 MΩ),VCC=VA=3.88 V、Vout=VB=3.88 V、VC=2.74 V、VD=1.40 V,电池静态输出电流为0.5 μA,V2管导通、V3管截止,V1管导通;VB接上4.36 V电源后,VC=2.72 V、VD=4.36 V,V2管弱导通、V3管导通(V3管漏源通道导通阻抗小于V2管),V1管截止,电池静态输出电流为0.2 μA(无倒灌电流流入电池)、VB接上4.36 V电源的静态输出电流为0.4 μA。两个偏置电阻分别焊接为100 MΩ,1 MΩ、100 kΩ,得到的测试结果与分立元器件无异,比较电路能够有效控制PMOS主管导通与截止,即能够通过大电流和具有防倒灌功能。

电路设计特性:

1)PMOS主管优选具有相同的参数、对称的集成PMOS辅管,可以保证温度变化时尽可能保持参数一致性。

2)根据不同损耗需求调整PMOS辅管两个漏极偏置电阻的大小,满足损耗需求。

3)整个电路静态损耗很低,电流损耗为小于微安级,若两个电阻串接更大电阻,静态电流损耗更小。

4)电路具有防止倒灌的功能,可以保护前级电路,且具有很低的正向导通电压。

5)PMOS主管可以使用不同导通电流的PMOS管,满足不同功率要求。

6)使用比较电路,电路简单,成本很低,实用性强。

7)特别适合于物联网NB-IoT超低损耗理想二极管电路应用,电路非常简单且具有很低成本。

5" 结" 论

PMOS辅管组成的比较器电路属于超低损耗控制器,与传统功率二极管或三极管控制电流损耗毫安级相比,静态电流损耗小两个数量级左右;与理想二极管(LTC4413)相比,静态损耗电流降低一个数量级左右,且不存在倒灌电流。使用本理想二极管电路大大降低了设备的静态损耗,延长了电池的工作时间,设备维护成本,损耗降低大,适合于物联网NB-IoT超低损耗理想二极管电路应用,电路很简单且具有很低成本优势。

参考文献:

[1] 胡志忠,王锐.含理想二极管电阻电路的分析 [J].电气电子教学学报,2011,33(3):109-111.

[2] 约翰逊,格雷厄姆.沈立等译.高速数字电路 [M].沈立,朱来文,陈宏伟,等译.北京.电子工业出版社,2008:32-33.

[3] 陈石平,林时君,庄桂玉,等.电子水尺低功耗处理电路设计 [J].电子技术,2018,47(1):36-38.

[4] 李明.防倒灌电流型安全电源系统设计与实现 [D].武汉:武汉大学,2017.

[5] Chew L H.理想二极管和热插拔控制器实现电源冗余并隔离故障 [J].电子技术应用,2013,39(3):9-11.

[6] 深圳市维创尼克科技有限公司.一种用单片机实现的防倒灌理想二极管:CN201720131224.5 [P].2017-08-29.

[7] 凌特推出双通道理想二极管LTC4413 [J].电子测试,2005(1):63.

[8] 陈石平,彭进双.一种超低损耗低端理想二极管:CN202010116370.7 [P].2020-09-22.

[9] 陈石平,彭进双.一种超低损耗理想二极管:CN202020206261.X [P].2018-08-14.

[10] 陈石平,彭进双.一种低损耗高端理想二极管:CN202020206281.7 [P].2020-09-22.

[11] 陈石平.晶体管电路设计 [M].北京.科学出版社,2024:100-110.

作者简介:陈石平(1981—),男,汉族,湖南郴州人,高级工程师,硕士,研究方向:嵌入式、物联网。