摘" 要:随着科技的不断发展,无人驾驶汽车产业成为一个新兴产业,保障驾驶安全成为研究热点之一。毫米波雷达凭借其大宽带、高分辨率、全天可用等特点脱颖而出,而RISC-V处理器因其开源、架构清晰、指令定制化程度高,被广泛应用于SoC设计中。文章设计了基于RISC-V的毫米波雷达信号处理系统,该系统能够对毫米波雷达采集的数据进行处理,将处理结果显示在电脑屏幕上,并且完成了相应的测试工作,验证了系统的可行性与有效性。

关键词:毫米波雷达;FPGA;RISC-V;LD2450

中图分类号:TN959 文献标识码:A 文章编号:2096-4706(2025)03-0032-05

Design of Motion Sensing Device Based on RISC-V Processor

LIU Chang, LIU Maoyang, ZHANG Yuqian, SHEN Jiacheng

(Portland Institute of NJUPT, Nanjing" 210023, China)

Abstract: With the continuous development of science and technology, the driverless car industry has become an emerging industry, and ensuring driving safety has become one of the research hotspots. The millimeter-wave radar stands out for its characteristics of large bandwidth, high resolution, and all-day availability, while the RISC-V processor is widely used in SoC design due to its open-source nature, clear architecture, and high instruction customization degree. This paper designs a millimeter-wave radar signal processing system based on RISC-V. The system can process the data collected by millimeter-wave radar and display the processing results on the computer screen. It completes the corresponding test work, verifying the feasibility and effectiveness of the system.

Keywords: millimeter-wave radar; FPGA; RISC-V; LD2450

0" 引" 言

伴随着科技的发展和汽车的普及,汽车的款式已从油车发展到混动车,部分城市甚至已经开始推广无人驾驶汽车。便利性上升的同时,安全问题也随之而来。带宽较大的毫米波雷达作为典型的车载传感器,凭借其较高的分辨率,在全天时、全天候都可以使用的特点,在高级辅助驾驶系统中发挥重要作用。而RISC-V处理器架构具有免费开源开放、整体的架构清晰易懂、指令定制化较高等特点,大量被应用在SoC(System on Chip)设计中,可以在保证集成化电路的前提前下,使用软硬件实现对安全问题的处理。

随着传感器技术和雷达成像算法的日益成熟,未来几十年汽车行业的竞争极大可能围绕着无人驾驶展开[1]。本文使用海凌科公司的LD2450型毫米波雷达作为前端传感器,基于E902 RISC-V处理器内核,设计并实现了一款运动感应装置,实验证明,该系统具有成本低、灵活性好,实时性高的特点。

1" 毫米波雷达工作原理

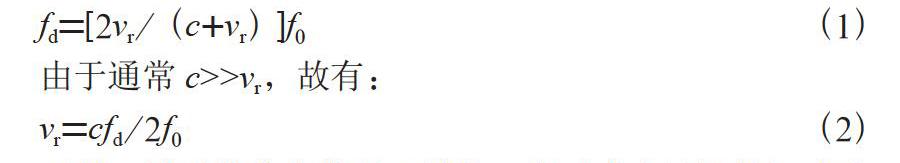

毫米波雷达系统通过发射电磁波信号,并接收反射回来的信号,来检测目标物体的位置、速度和角度。雷达系统从其发射天线发射FMCW(Frequency Modulated Continuous Wave)信号,如图1所示。根据FMCW测距理论,当雷达信号遭遇目标物体后,信号在物体处产生发射,目标反射的回波信号与雷达的发射信号存在频率差[2]。

当信号打到一个物体时,部分信号能量被反射回雷达的接收天线,混频器将发射信号和接受信号混合在一起。混频器将两个信号合并到一起生成一个具有新频率的新信号。把由信号传播引起的时间延迟记为τ,其表示为信号从雷达发射到目标、反射回雷达所需的时间可由式(1)所得:

(1)

式中,R为雷达与目标物体的距离,c为光速。最后将混频器生成的信号经过低通滤波器保留我们需要的频率的信号。毫米波雷达一般发射具有大的时宽带宽积的线性调频信号,假设信号周期为T,差频信号频率、时间延迟与调制周期和带宽之间的关系如式(2)所示:

(2)

综合式(1)和式(2),根据FMCW原理所得被测物体的距离可如式(3)所示[3]:

(3)

2" 系统设计

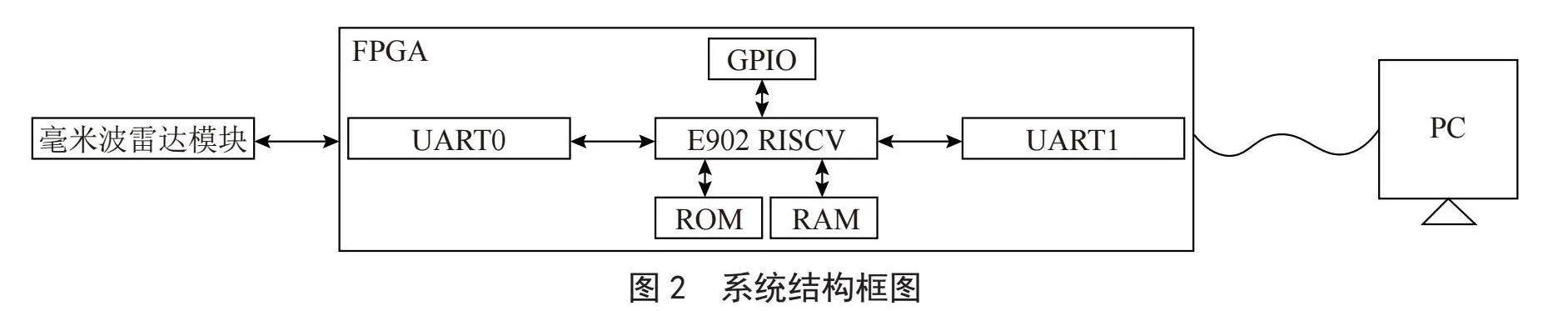

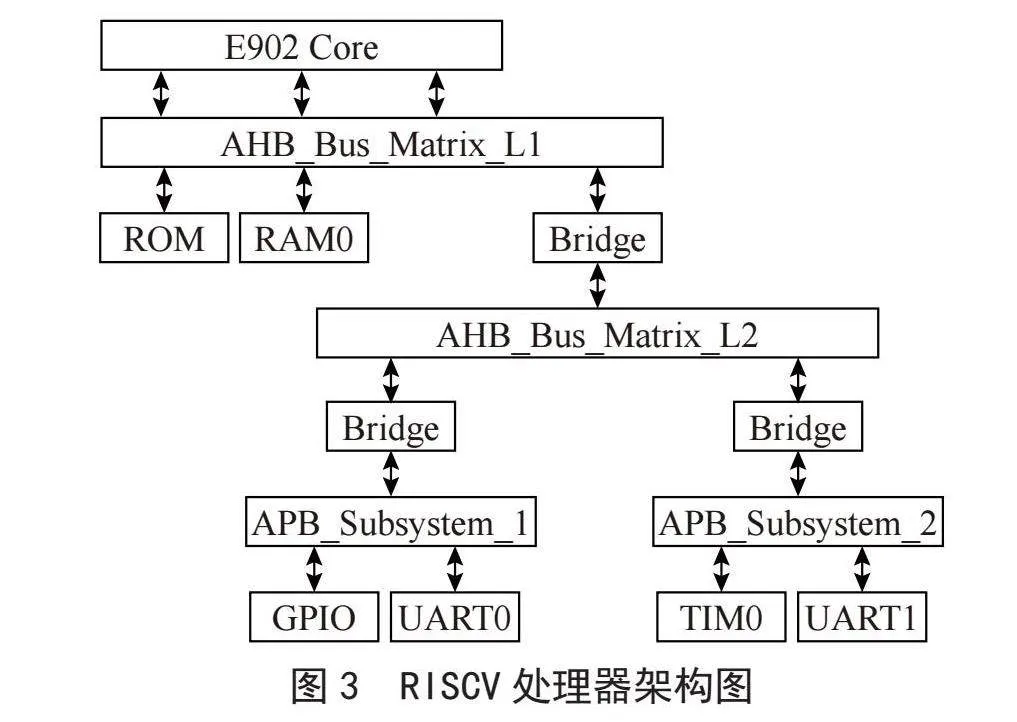

本装置由LD2450毫米波雷达传感器、RISCV处理器、PC上位机构成,系统的整体结构如图2所示。其中,RISCV处理器由“平头哥”的E902 32位微处理器内核,两级AHB总线矩阵、AHB2APB转换桥、ROM程序存储器、RAM数据存储器、UART控制器、GPIO控制器等模块构成。ROM、RAM存储器通过AHB接口挂载在AHB总线矩阵上,UART和GPIO控制器通过AHB2APB转换桥挂载到AHB总线矩阵,整个RISCV处理器系统由FPGA可编程逻辑芯片实现,RISCV处理器的系统架构如图3所示。

运动目标跟踪是指在特定区域内实时监测和定位运动目标的位置,并实现测距、测角和测速功能。LD2450是海凌科24 GHz毫米波雷达系列中的一款运动目标跟踪传感器模组,集成了简化的24 GHz雷达传感器硬件和智能算法固件。该方案主要用于普通场景下的运动人体定位跟踪。传感器硬件包括AloT毫米波雷达芯片、高性能一发两收微带天线、低成本MCU及外围辅助电路。智能算法固件采用FMCW波形和雷达芯片专有的先进信号处理技术。该传感器支持串口输出检测数据,即插即用,能够灵活应用于各种智能场景和终端产品。

E902处理器内核采用了16/32位混合编码系统,拥有2级极简流水线,广泛应用于低功耗的IoT场景。其中LD2450传感器负责检测移动目标,将目标的方位、速度、距离指令通过串口实时地传给RISCV处理器,RISCV处理器内核通过AHB总线矩阵,访问UART0控制器,读取LD2450的数据并且进行解析,并且将解析后的各目标的坐标值通过UART1上传给PC上位机。

3" 运动感应装置的软硬件设计与仿真

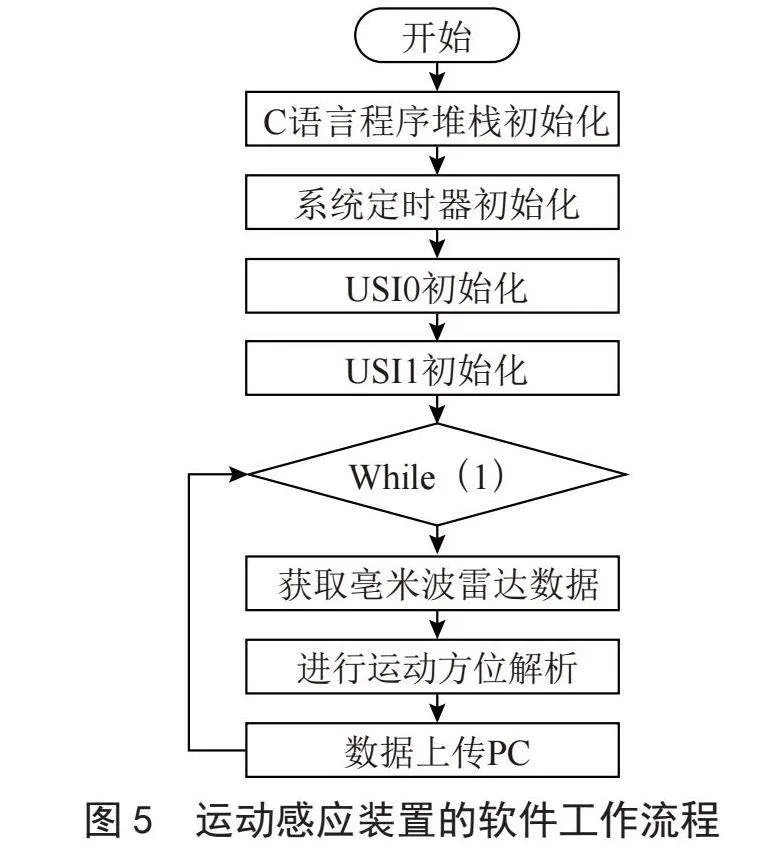

本设计采用软硬件协同的方式,对用到的RISCV处理器进行设计,其中硬件部分以FPGA为平台,使用Vivado进行Verilog语言设计,用FPGA内部的逻辑资源对RISCV处理器内核、AHB总线矩阵、ROM程序存储器、RAM数据存储器、AHB2APB转换桥、UART控制器、GPIO控制器、定时器等模块进行模拟实现,其中涉及搭建E902 RISCV处理器工程并添加“平头哥”提供的E902处理器的Verilog文件,并且用VIVADO自带的ROM IP核Verilog中的ROM存储模块进行替换,同时采用VIVADO的PLL锁相环模块产生RISCV处理器所需要的系统时钟。设计中,处理器的系统时钟采用26 MHz。软件部分RISCV处理器的C语言运行程序则是由“平头哥”提供的CDK嵌入式软件设计平台进行实现,程序中主要完成系统堆栈初始化、系统定时器初始化、串口0初始化、串口1初始化、毫米波雷达数据的解析以及将坐标方位信息上传到PC上位机。硬件和软件的设计流程分别如图4、图5所示。

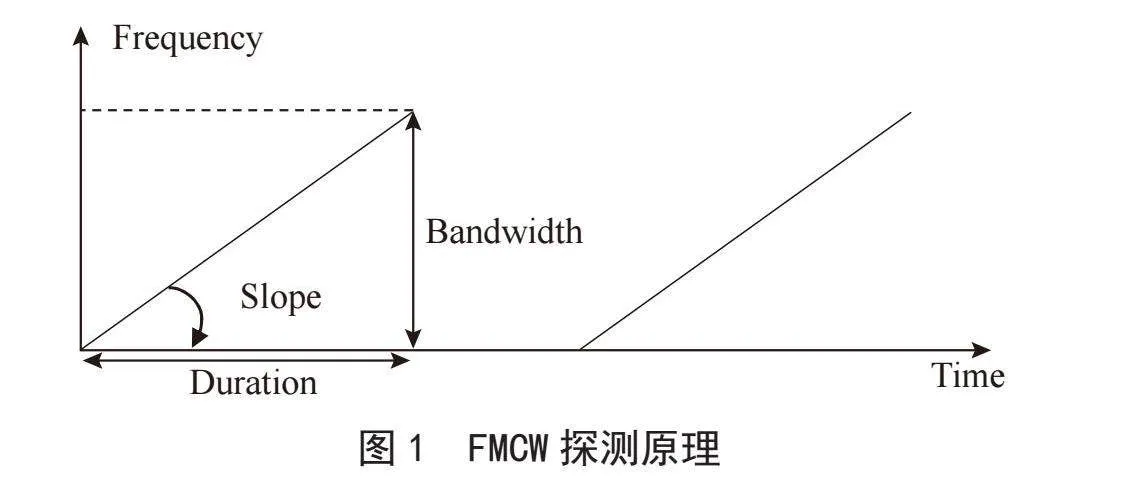

通过编写RISCV处理器的TestBench激励文件,来对所设计的RISCV处理器进行软件行为仿真。利用VivadoHLS可以缩短1/3的RTL仿真时间,使算法验证速度提高10倍以上[4]。其中,TestBench主要负责产生RISCV处理器工作所需的系统时钟、复位信号以及初始化处理器运行所需的ROM程序[5]。

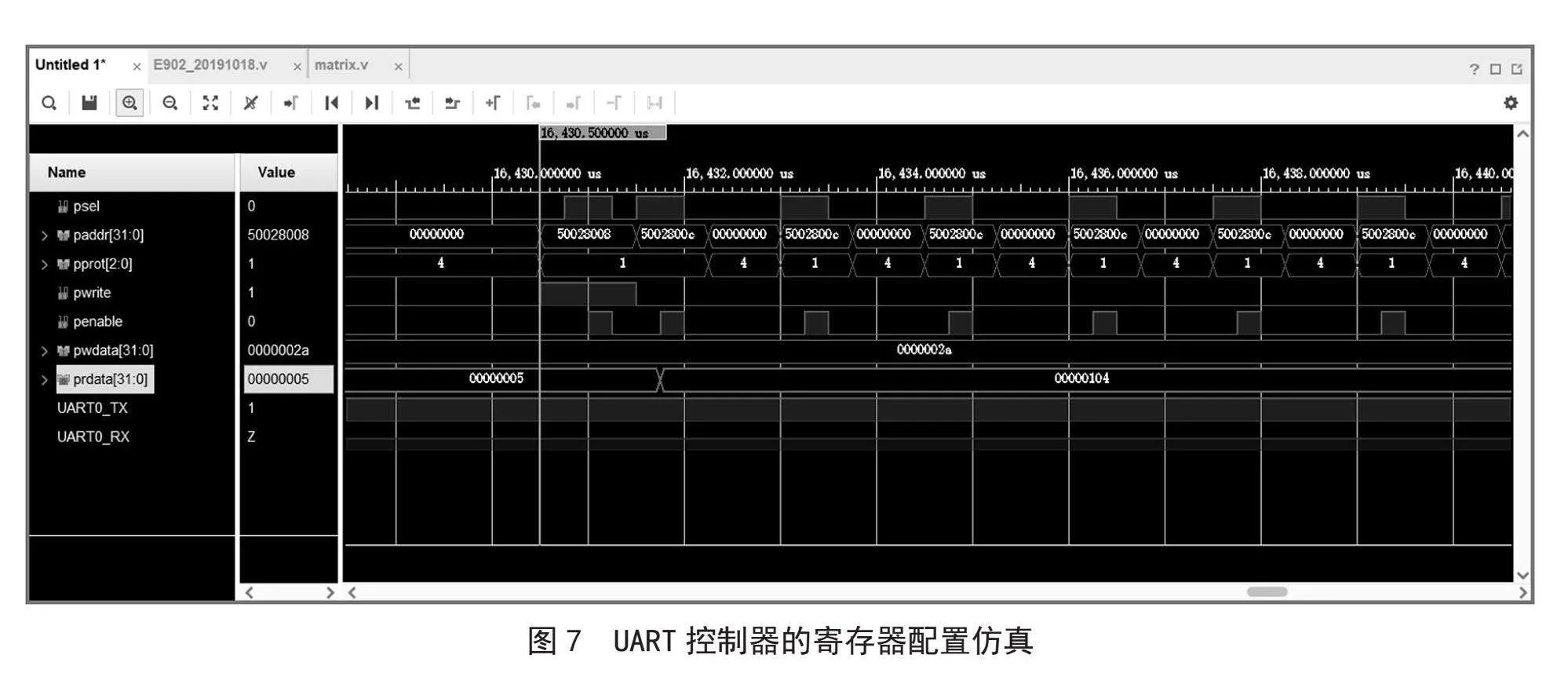

行为仿真主要是用来检验RISCV系统是否能正常运行C语言程序,因此观察仿真波形时将重点关注ROM存储器接口上是否有读取操作的信号以及UART控制器的APB口上是否有读写信号,这些读写信号表示USI0的初始化寄存器配置信号[6]。RISCV处理器的ROM、UART接口的仿真波形分别如图6、图7所示。

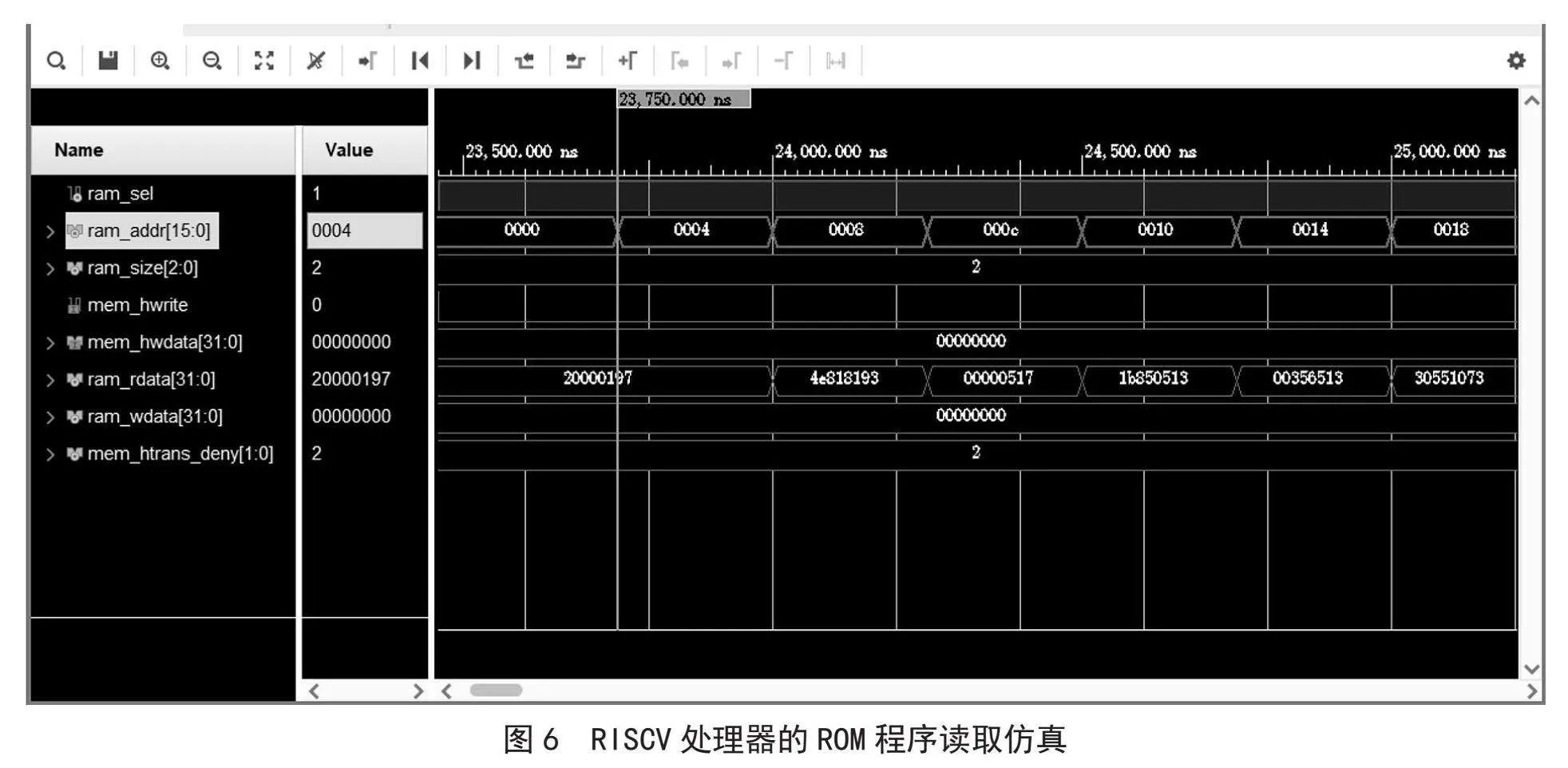

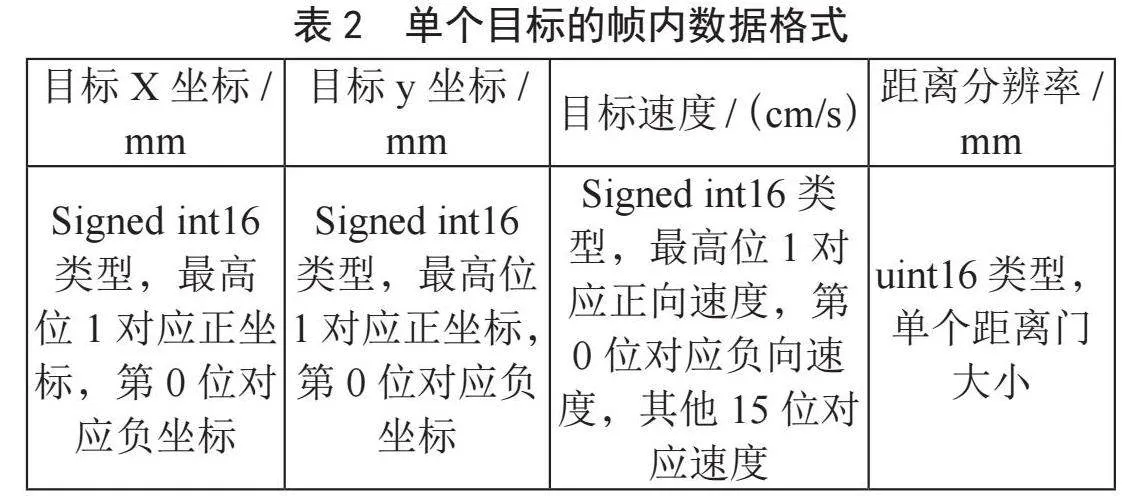

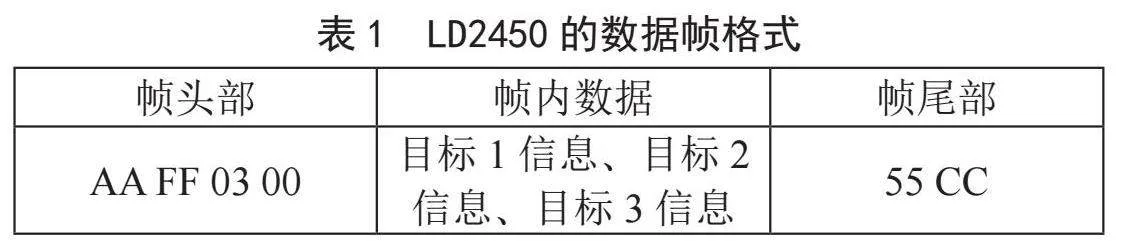

当LD2450毫米波雷达模块探测到外部的移动物体时,会将物体的运动信息,以十六进制的帧格式从UART串口输出,一帧数据共包含三个移动物体的信息,具体分为帧头信息,目标1的二维坐标信息、速度信息以及距离精度信息,目标2的二维坐标信息、速度信息以及距离精度信息,目标3的二维坐标信息、速度信息以及距离精度信息,帧尾信息。RISCV处理器使用UART0接口对LD2450的UART信号进行接收,并通过AHB2APB转换桥送往RISCV处理器的AHB二级总线矩阵,并通过AHB2AHB同步桥送往一级AHB总线矩阵直至送到RISCV处理器内核,RISCV处理器获取到十六进制的运动信息后将对其进行解析,分别得到目标的二维坐标、运动速度以及距离精度等信息[7]。LD2450输出的十六进制帧格式信息如表1所示,帧内的每个目标方位信息的格式如表2所示。

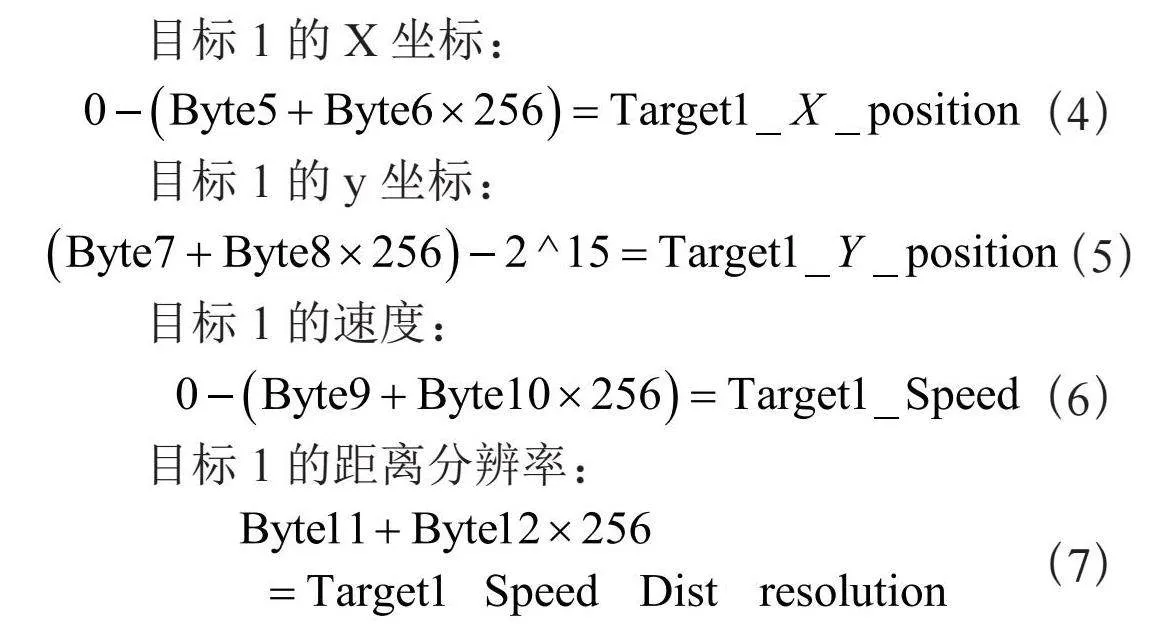

该数据帧的前4个字节表示帧头信息、尾部两个字节表示帧尾信息,字节5~字节12表示目标1的二维坐标信息、速度信息以及距离分辨率信息。字节13~字节20表示目标2的信息,值为0则表示探测区域中没有第二个移动目标。字节5~字节12所对应目标1的X、Y坐标,速度以及距离分辨率的转换如式(4)至式(7)所示。

目标1的X坐标:

(4)

目标1的y坐标:

(5)

目标1的速度:

(6)

目标1的距离分辨率:

(7)

4" 系统实物与测试

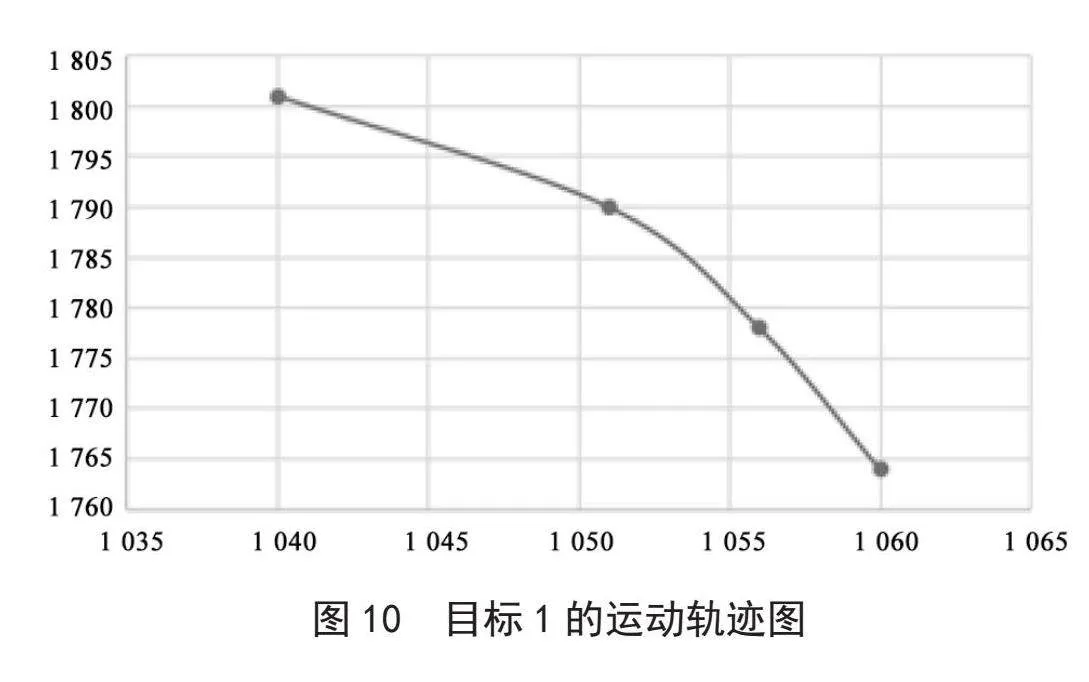

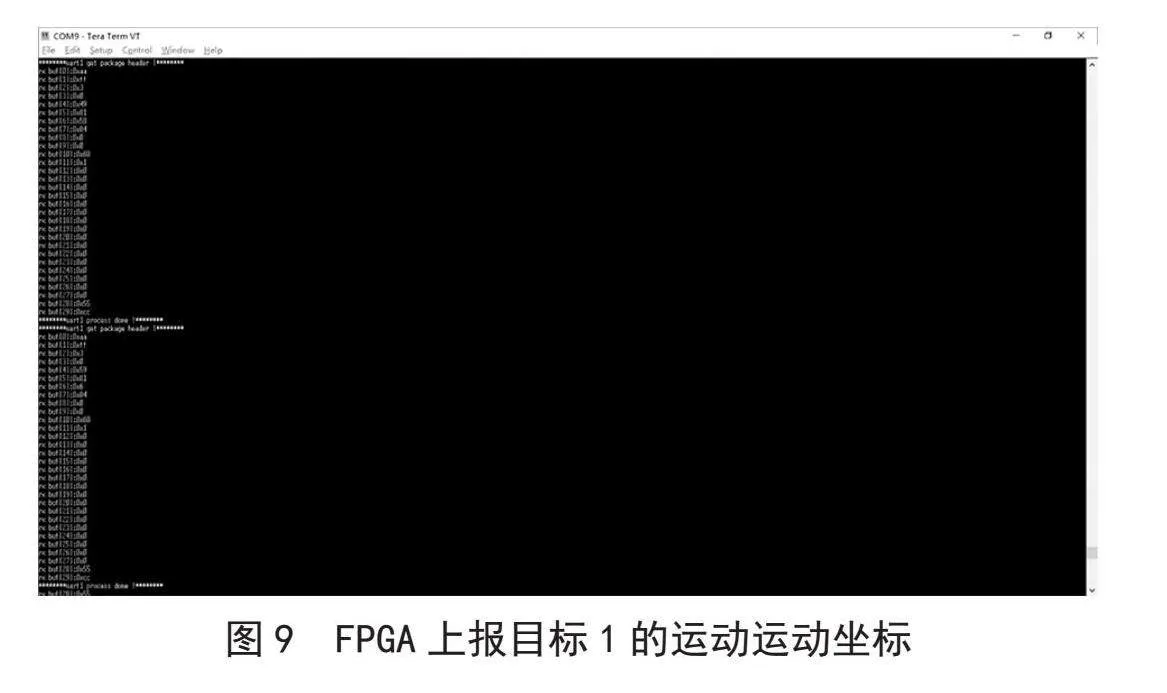

系统实物由FPGA开发板、LD2450毫米波传感器、USB转UART模块、CKLink调试器以及电源线等构成。完成各部分电路的连接之后对系统进行功能测试。测试中将FPGA开发板与PC上位机相连,使用Teraterm串口调试助手对FPGA上传的运动目标的方位等信息进行查看[8-10]。系统实物如图8所示,FPGA上报的运动坐标如图9所示,在PC上位机根据FPGA上传的人体运动坐标进行绘制,所得的行动轨迹与测试中人体行走轨迹基本一致,测试的人体运动轨迹如图10所示。

5" 结" 论

本文以FPGA为平台,使用其内部的可编程逻辑资源模拟了平头哥的E902 RISCV处理器,基于该处理器和LD2450毫米波雷达模块设计了一款运动感应装置,实现了对运动目标的二维方位坐标和速度的探测,并且将最终的方位信息上传到PC上位机。实验结果表明该装置能够实现高精度的运动检测和实时数据处理,具有集成度高、实时性好等优点。

参考文献:

[1] 王佳慧,杨果,王雨晗,等.基于MSER的车载毫米波雷达SAR图像目标检测 [J/OL].现代雷达,2024:1-10[2024-07-16].http://kns.cnki.net/kcms/detail/32.1353.TN.20230920.1115.002.html.

[2] 罗诗敏,龙诺春.基于FMCW毫米波雷达的复杂场所测距系统研究与设计 [J].电子制作,2023,31(13):80-83.

[3] 李嘉浩,姚金杰,姬娜娜,等.基于ARM的高精度毫米波雷达测距传感器 [J].单片机与嵌入式系统应用,2022,22(11):58-61+69.

[4] 张锐浩,李晓琪,党立志,等.Vivado HLS的图像传感器FPN噪声去除算法设计 [J].单片机与嵌入式系统应用,2023,23(12):55-58+62.

[5] 张艳辉,郭洺宇,何宾.VivadoHLS嵌入式实时图像处理系统的构建与实现 [J].电子技术应用,2016,42(9):115-117+121.

[6] 杨博,楚要钦,景德胜,等.基于 AXI4总线的 SoC中离散量信号控制IP核的设计与验证 [J].信息通信,2020,2020(3):90-92.

[7] PROBST F,ENGELMANN A,DIETZ M,et al. An Area Efficient Low-Power mmWave PRBS Generator in FDSOI [C]//2022 IEEE/MTT-S International Microwave Symposium(IMS 2022).Denver:IEEE,2022:283-286.

[8] PETERS S,FAGHIH-NAINI S,ERHARDT S,et al. A Planar V-Band Antenna for Wideband Radar and Communication on Low-Cost PCB Substrate [C]//2023 IEEE Radio and Wireless Symposium (RWS).Las Vegas:IEEE,2023:153-155.

[9] FAGHIH-NAINI S,PETERS S,KURIN T,et al. Transceiver Setup for Joint Communication and Sensing Applications in V-Band [C]//2023 IEEE Radio and Wireless Symposium (RWS).Las Vegas:IEEE,2023:118-121.

[10] AHMED M K,BOBDA C. ISO-TENANT: Rethinking FPGA Power Distribution Network (PDN): A Hardware Based Solution for Remote Power Side Channel Attacks in FPGA [C]//Monterey:Association for Computing Machinery,2024:42.

作者简介:刘畅(2003—),男,汉族,江苏盐城人,本科在读,研究方向:电子科学。