中图分类号:TN711;TN713 文献标识码:A 文章编号:2096-4706(2025)08-0029-05

Abstract:Digital control circuits constitute one of the components of the radar receiver system. Under the same functionaldesign,inordertorducethepowerconsumptionofthecoredeviceFPGAofthedigitalcontrolcircuitwithnthefull temperaturerange,thedesignofthedigitalcontrolcircuit isoptimized.Comparativedesignsareconductedfordomestic FPGA devices JFM7K325T and JFMK50T4.It can beobtained that the power consumption of JFM7K325T at normal temperature isapproximately 2 . 3 W ,and within the full temperature range (-40 to  ),the power consumption reaches1.9 to 8 W, and the maximum current required bythecorevoltageis2A.Thepowerconsumptionof JFMK5OT4 atroom temperature is only 1.175 W, and the maximum power consumption reaches 2 . 8 W within the full temperature range. Under the same environmental temperature,the power consumption is decreased by 1 / 2 to 3/4.The power supply design, thermal design,and spatial design of the chips are significantly reduced, and the cost of a single chip can also be lowered by 2/3.

),the power consumption reaches1.9 to 8 W, and the maximum current required bythecorevoltageis2A.Thepowerconsumptionof JFMK5OT4 atroom temperature is only 1.175 W, and the maximum power consumption reaches 2 . 8 W within the full temperature range. Under the same environmental temperature,the power consumption is decreased by 1 / 2 to 3/4.The power supply design, thermal design,and spatial design of the chips are significantly reduced, and the cost of a single chip can also be lowered by 2/3.

Keywords: domesticization; FPGA; low power consumption; digital control circuit

0 引言

雷达接收机系统中数字控制电路常用的FPGA芯片为Xilinx公司的XCK325T(以下简称K7),其优点包括IO资源丰富、高速口通道多、体积合理。而在当前国产化背景下[1],对标Xilinx公司K7的为复旦微电子公司的FPGA芯片 J F M7 K3 2 5 T 。经实测,其常温下功耗为 5 ~ 8 W ,在高低温环境下,其内核电源电压所需电流会增加到常温的2~3倍,辅助电源电压所需电流会增加到常温的 1 . 5 ~ 2 倍,总功耗增加1倍[2]。在此背景下,对数字控制的功耗冗余、元器件散热以及器件稳定性等性能要求更高[3]。

本文选用的国产FPGA芯片为复旦微电子公司JFMK50系列的  ,验证结果表明,在同等应用条件和使用功能下,其低功耗特性可有效降低给FPGA供电电源芯片性能要求、器件成本及板上使用面积,以及器件响应时间。

,验证结果表明,在同等应用条件和使用功能下,其低功耗特性可有效降低给FPGA供电电源芯片性能要求、器件成本及板上使用面积,以及器件响应时间。

1国产器件调研与选型

2023年,经调研,海外厂商Xilinx、Intel、Lattice、Microchip位居世界前四[5],遥遥领先。而在当前国产化背景下,经过调研与比对,国内FPGA厂商主要有:紫光同创、复旦微电子、高云GOWIN、华微、京微齐力、上海安路等。通过对比选型,其中复旦微电子公司成立时间较早,成立于1998年,该公司正向研发设计实力雄厚,开发工具可完全嵌套Xilinx公司的开发工具VIVADO,采用业内先进的CMOS工艺制程,其 2 8 n m 芯片是国内最早研制成功的亿门级芯片[。

本文选用的复旦微电子公司的JFMK50系列FPGA芯片JFMK50T4-N,其特点为低功耗、低成本、小尺寸封装,可灵活配置组合编程资源,具备实现输入输出接口、通用数字逻辑、存储器、时钟管理、数字信号处理等多种功能[],同时提供丰富的专用时钟与布线资源,便于实现高速、复杂的数字逻辑电路,在数据中心、人工智能、自动驾驶、工业控制、信息处理、仪表测量等领域广泛应用[8-9]。

JFMK50T4-N(以下简称A7)芯片内部包含可用于实现数字逻辑控制和分布式RAM的CLB模块,还包含BlockRAM、DSP、I/O、MMCM、GTX等可编程逻辑模块,可以方便地实现可编程逻辑控制应用[10]

2数字控制电路总架构

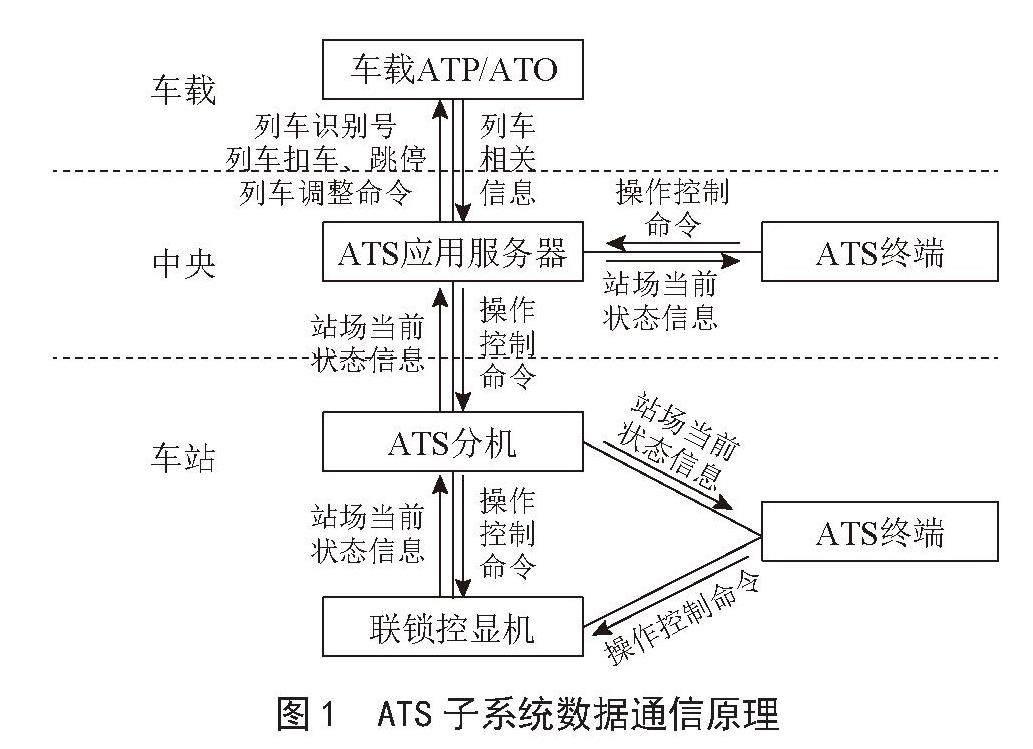

数字控制电路是雷达接收机系统的核心电路[1],接收机的核心为ADC模块,负责将模拟信号转换为数字信号,然后由数字接口传递给FPGA进行处理,本文主要研究的是接收机数字控制电路[12]。雷达接收机系统前端链路如图1所示,其主要由天线、射频分机、中频分机、信号处理机组成,天线负责接收所需工作范围内的工作信号,将接收的电磁波转换为电信号传达给射频分机;射频分机将工作信号的频率进行放大、变频后传输给中频分机,中频分机再将工作信号的频率进行下一步的放大、变频,模数转换后,回传数据给信号处理机,并接收信号处理机给出的控制指令,对射频分机、中频分机进行一系列的控制及数据处理,中频分机的数据处理及控制等功能,均由数字控制电路完成。以FPGA为核心的数字控制电路包含在中频分机,本文着重研究数字控制电路部分。

图1雷达接收机系统前端链路

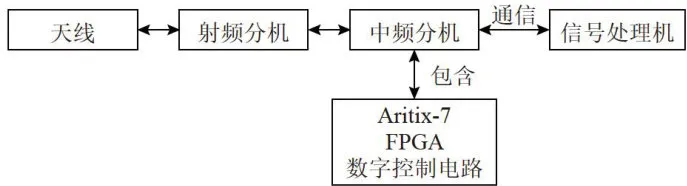

图1雷达接收机系统前端链路FPGA作为数字控制电路关键器件,其可响应信号处理机给的一系列指令,做出相应处理后,将检测的中频分机、射频分机的信号数据经解算、处理后回传给信号处理机[13],其系统架构如图2所示。

图2中,A7需要晶振提供参考时钟,晶振的频率为 1 0 M H z ,这是控制电路的工作来源。在此基础上,A7还需要配置FLASH进行程序存储,防止掉电后丢失控制程序,A7还对接收机系统中的中频分机、射频分机模拟链路进行电源管理,在中频分机、射频分机需要工作的时候进行加电、断电管理。A7还对中频分机进行一系列处理及回传数据给信号处理机,主要包括:分机内部的时序控制、工作信号频点跳频、工作信号采样、工作信号幅度检波、分机内部温度检测及上报、工作信号增益的温度补偿、工作信号增益补偿等。

A7还具备对射频分机回传的接收信号及数据进行时序控制、读取并上报射频分机的温度检测和幅度检测的功能。A7与信号处理机之间的通信采用速率较快的串口进行通信,该通信速率满足雷达接收机系统的通信速率要求,大约为10Mbit/s。

图2数字控制电路系统架构

图2数字控制电路系统架构3 芯片A7上电顺序设计

为了保持A7在上电时的电流达到最小,正常工作时保证低功耗性能,其工作时必须确保满足一定的上电顺序。芯片A7所需的加电电压为VCCCORE(1.0 V)、VCCHRAM(1.0V)、VCCSUP(1.8V)、VCCP(3.3V),其上电顺序为:VCCCORE(内核电压)、VCCHRAM(RAM块电压)、VCCSUP(辅助电压)、VCCP(I/O电压)。为保证耐压风险,其中VCCP必须保持推荐的上电顺序,且VCCCORE和VCCHRAM可以合并供电 1 . 0 V 。本设计中不涉及高速通道的GTX收发器,故不存在UHSTVCC、UHSTVTT供电顺序。如图3所示,本文采用江苏展芯公司的电源芯片XC98321、XC9884给芯片A7供电。本设计方法中,选用的电源芯片XC98321为DCDC开关电源,具有双路电压输出,其中一路的同步整流电路可输出2.5A平均电流,输出电压范围为  ,输出电压误差为± 1 . 8 5 % ,并且具有完善的保护功能,包括短路保护、热保护和峰值电流保护,保证了工作的可靠性。选用的展芯公司的电源芯片XC9884,可同步整流输出4A平均电流,它带有输出电压状态指示脚PG脚,可进行上电指示。同时,XC98321、XC9884存在固有的转换时间(约为 1 0 m s 、 1 2 m s ),保证了A7严格的供电顺序。

,输出电压误差为± 1 . 8 5 % ,并且具有完善的保护功能,包括短路保护、热保护和峰值电流保护,保证了工作的可靠性。选用的展芯公司的电源芯片XC9884,可同步整流输出4A平均电流,它带有输出电压状态指示脚PG脚,可进行上电指示。同时,XC98321、XC9884存在固有的转换时间(约为 1 0 m s 、 1 2 m s ),保证了A7严格的供电顺序。

4A7芯片配置设计

芯片A7有7种配置模式,本文选择主串配置模式,其电路如图4所示,还包括A7的下载及引导程序电路。其中,TCK、TMS信号端需上拉 1 0 kΩ 电阻,保证了无Cable信号接入时,信号维持高电平;C2、C3处的 0 . 1 μ F 和 2 2 μ F 电容是为了滤除电源端会引入的纹波杂散,L1、L2处磁珠的作用是抑制电路中的高频噪声,CCLK信号必须走 5 0 Ω 匹配阻抗。同时,该芯片采用JTAG配置模式进行在线调试,JTAG配置模式比其他配置模式优先级都高,JTAG接口为业内标准接口,但A7芯片下载器的接口为插针式接口,使用不便,故使用X6下载口进行转换,X6的作用是将下载器的JTAG接口变为业内常用的电气接口矩形连接器进行连接。本设计选用的是9芯的矩形连接器进行转换,该矩形连接器既保证了JTAG接口的标准通信,又保证了下载程序接口的通用性。

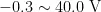

5 配置芯片电路设计

选用的FPGA配置芯片是EFM25F128A,是一款串行SPIFlash存储器,属于非挥发性存储器,可多次读出与写入,具有在器件的电源掉电之后,仍旧能存储数据信息的强大特点。该芯片体积小,工作时钟频率高,读写及引导速度快,可靠性高,擦写次数可达1万次,数据可保存20年,支持低功耗模式,典型待机电流为 1 μ A ,典型活动电流为 1 2 m A ,工作模式选用主四口SPI配置模式,硬件原理图如图5所示。其最大读写速度可达 3 3 M H z ,通过实际测试,将工作时钟设置为 2 2 M H z 时,该时钟范围合理,留有空间,其板上引导程序时间约为 2 s ,远小于系统要求响应时间。

图4FPGA芯片配置电路

图4FPGA芯片配置电路6A7上电时间及工作电流实测结果

A7实测上电时间如图6所示,VCCCORE和VCCHRAM的上电时间为 1 7 . 5 m s ,VCCSUP的上电时间为 2 2 . 2 m s ,VCCP的上电时间为 2 4 m s , + 5 Δ V 电压上电时间为 3 3 m s ,晚于A7上电时间,满足器件本身设计要求。

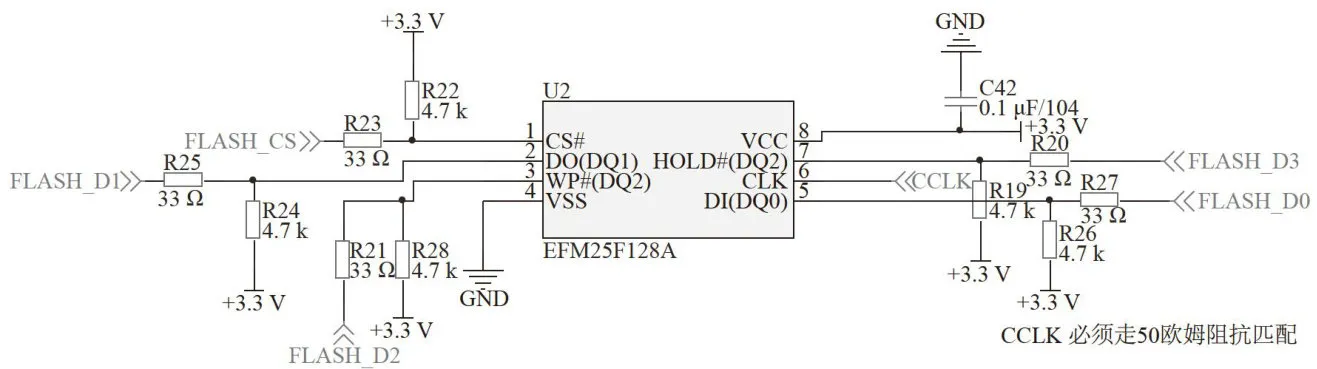

A7与K7的常温功耗对比如表1所示,由表1数据可得,进行同等要求的控制、时序、回传数据等同等功能设计时,常温环境下,K7的工作电压

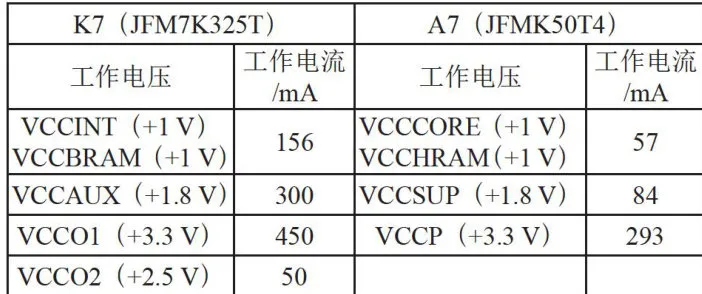

VCCINT和VCCBRAM的电流为 1 5 6 m A ,VCCAUX的电流为  ,VCCO1和VCCO2的电流分别为 4 5 0 m A , 5 0 m A ;A7的工作电压VCCCORE和VCCHRAM的电流为 5 7 m A ,VCCSUP的电流为8 4 m A ,VCCP的电流为 2 9 3 m A 。因此,A7功耗仅为1.175W,而K7为 2 . 3 0 6 W ,K7功耗是A7的2倍。全温范围内,板上供电电压为 1 2V ,其实测电流如表2所示,由表2可得,供电电压为 1 2V 时,K7全温功耗为 1 . 9 ~ 8 . 0 W ,A7全温功耗为 0 . 9 ~ 2 . 8 W 。

,VCCO1和VCCO2的电流分别为 4 5 0 m A , 5 0 m A ;A7的工作电压VCCCORE和VCCHRAM的电流为 5 7 m A ,VCCSUP的电流为8 4 m A ,VCCP的电流为 2 9 3 m A 。因此,A7功耗仅为1.175W,而K7为 2 . 3 0 6 W ,K7功耗是A7的2倍。全温范围内,板上供电电压为 1 2V ,其实测电流如表2所示,由表2可得,供电电压为 1 2V 时,K7全温功耗为 1 . 9 ~ 8 . 0 W ,A7全温功耗为 0 . 9 ~ 2 . 8 W 。

表1常温( 下K7与A7的功耗对比

表1常温( 下K7与A7的功耗对比

表2全温范围K7与A7的PCB板上电流对比

表2全温范围K7与A7的PCB板上电流对比由此可得,在控制及通信条件同等满足的情况下,A7与K7相比,A7可降低功耗 1 / 2 ~ 3 / 4 ,满足了接收机系统低功耗的要求,降低了工作电流、空间占用、板上面积、热损耗等,提高了电路的响应速率及缩短了程序引导时间,为低功耗数字控制电路提供了更优的设计方案。此外,单只JFMK50T4的价格约为JFM7K325T的1/3,价格成本优势明显。

7结论

数字控制电路作为雷达接收机系统中的重要组成部分,本文以低功耗Artix-7FPGA为核心器件,搭载了高速率编解码器EFM25F128A及高速率AD转换器等器件,设计了一个工作效率较高、响应迅速的电源电路,严格保证了控制电路的上电时序及功耗。

本文提出的一种基于低功耗FPGA的硬件数字电路架构,具有简单灵活、可靠有效、成本低廉等应用优势,解决了低功耗、低热耗、低成本、响应快等问题,系统工作稳定可靠,反应速度快,具有较高的应用价值和使用前景。

参考文献:

[1]梁丽.基于EDA技术的电子线路设计的改革与实践[J].实验技术与管理,2020,37(2):100-103+116.

[2]刘仲方.CMOS电路低功耗设计与优化研究[D].杭州:浙江大学,2015.

[3]王祚栋,魏少军.SOC时代低功耗设计的研究与进展[J].微电子学,2005(2):174-179.

[4]李杰,李一轩,吴天生,等.基于FPGA无人机影像快速低功耗高精度三维重建[J].北京航空航天大学学报,2021,47(3):486-499.

[5]朱鹏程,胡娜.基于APU  FPGA的机载视频和通讯总线处理系统设计[J].电光与控制,2021,28(5):98-102.

FPGA的机载视频和通讯总线处理系统设计[J].电光与控制,2021,28(5):98-102.

[6]袁春辉,周建江,董琏.基于FPGA的机载视频显示系统的低功耗设计[J].现代电子技术,2015,38(12):89-91.

[7]孙艳萍,李孟,屈文涛.基于国产FPGA的射频数据采集及处理系统设计[J].机电工程技术,2023,52(4):128-132.

[8]杨德振,李凯峰,蔡佳一,等.基于国产FPGA的红外图像处理算法实现[J].激光与红外,2022,52(8):1223-1229.

[9]王鑫华,陈明辉,杨格亮.L波段四通道发射电路芯片的设计与实现[J].半导体技术,2018,43(7):504-509.

[10]郑东卫,白亚莉.基于FPGA和多核DSP的雷达信号处理架构设计[J].火控雷达技术,2023,52(2):84-90.

[11]刘成,彭思,林选锋.基于FPGA与DSP架构的接收机设计[J].电子设计工程,2023,31(3):141-144.

[12]蔡勇超,余勇.基于FPGA和单片机的数字中频收发机设计[J].信息技术与信息化,2023(6):147-150.

[13]黄伟,王雷,吴军锋.基于FPGA的数字中频信号处理平台的设计与实现[J].现代导航,2017,8(6):422-426.

作者简介:徐亚维(1991一),女,汉族,雅安人,工程师,硕士,研究方向:雷达控制电路设计。