刘文元

(中国电科网络通信研究院,河北 石家庄 050011)

0 引 言随着物联网时代的到来,嵌入式系统的以太网设备需求量与日俱增,而负责以太网数据编码和传输的物理层收发器的需求量也随之增长。在加快集成电路产业自主可控步伐的趋势下,PHY 芯片的研发工作正如火如荼地进行。

芯片的测试工作,是芯片在流片完成之后,交付给客户之前的重要一环,旨在验证芯片的硬件功能,为终端用户提供驱动程序的代码原型。在产业实践中,对于PHY 的UVM验证工作虽有文献可参考,但对于PHY 芯片的板级测试问题,尚无统一的标准,需要开发者自己按照PHY 的数据手册编写驱动。若没有PHY 芯片厂商提供直接的技术支持,调试过程就会面临苦难。

考虑到用户可能会面临的PHY 调试问题,基于一款自主研发的GPHY(Gigabit Physical Layer Transceiver)的功能验证工作,本文首先介绍了GPHY 测试系统的架构,也即GPHY 的典型使用场景;然后着重论述了测试程序的设计,提出了将数据分阶段loopback 的测试方法;最后展示了测试过程中的系统日志和基于LwIP 的网络实验结果。希望能为同行的以太网PHY 功能测试和应用开发提供参考经验。

1 测试系统架构以太网是遵守IEEE 802.3 标准的局域网,TCP/IP 参考模型中的物理层(PHY)一般由专用的数模混合集成电路来实现,即PHY 芯片,而与之直接交互的就是数据链路层中的介质访问控制子层(MAC),因此PHY 芯片的功能验证离不开MAC 的支持。

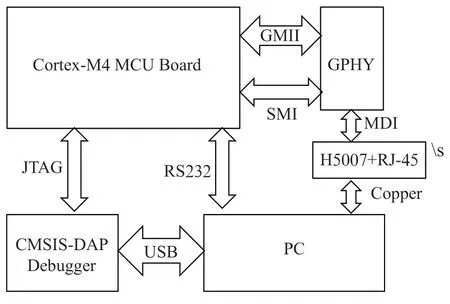

为了验证GPHY 的功能,本文选取了一种基于Cortex-M4 内核的32 位微控制器(MCU),它的APB 总线上挂载的以太网外设模块支持千兆速率MAC(GMAC)的功能。以太网外设模块中还集成了站管理接口(SMI),专门用于和外部PHY 之间的通信,以访问PHY 芯片的寄存器。MCU 与GPHY 通过标准的千兆介质独立接口(GMII)来连接,GMII 提供了时钟和数据的传输途径。

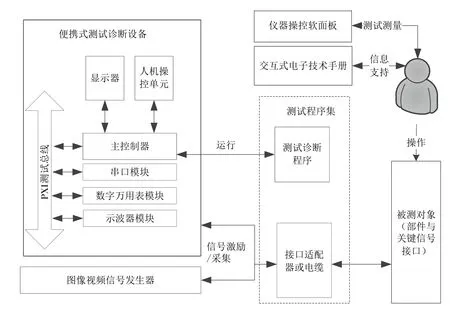

为便于在线调试和单步跟踪,选择了使用非常广泛的Keil-5 作为测试程序的开发环境,该环境自带了交叉编译工具,方便用户移植本测试程序到特定的应用场景。程序的在线调试与跟踪依赖调试器CMSIS-DAP Debugger,它通过Jtag 接口与MCU 相连接,通过USB 接口与PC 相连接。此外,MCU 的UART 通过RS232 与PC 的串口相连接,在PC端开启串口调试助手,可以查看包括了程序运行状态、PHY寄存器状态和测试信息的系统日志。PC 机上的网线通过水晶头插在RJ-45 上,RJ-45 与PHY 芯片之间有一个负责电压变换的器件H5007,二者之间的引线MDI+/-上传输的是差分信号。GPHY 测试系统的架构图,如图1所示。

图1 GPHY 测试系统架构图

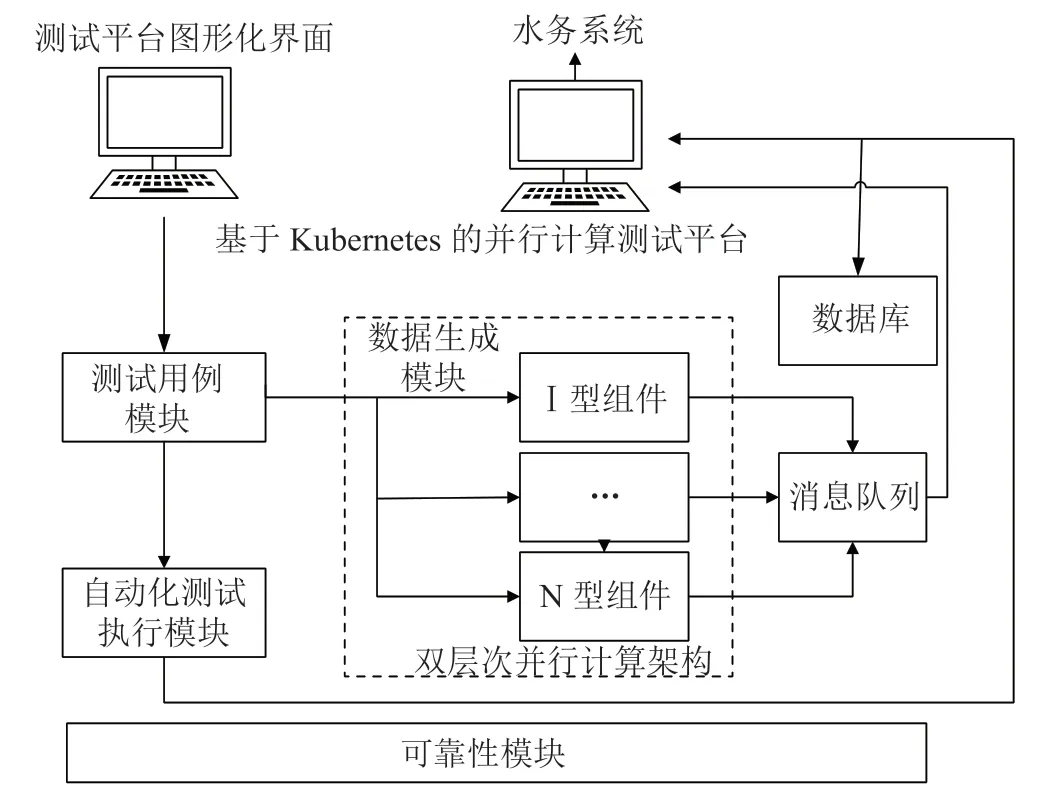

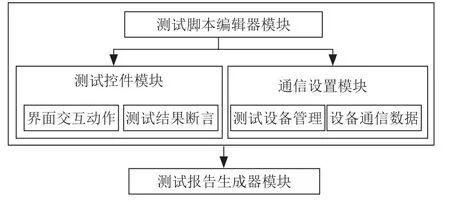

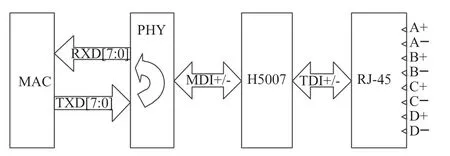

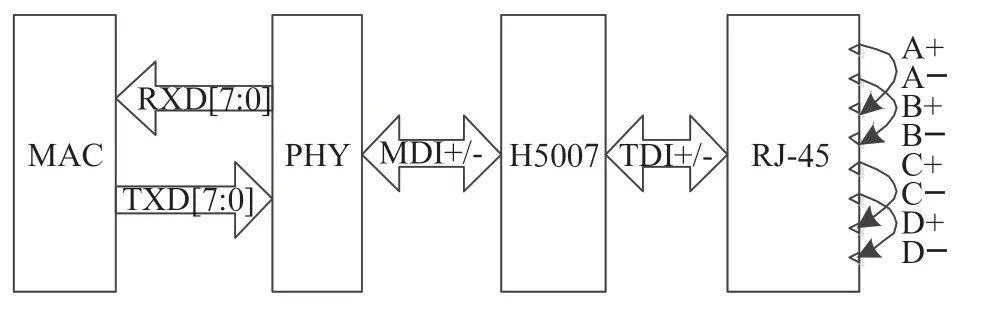

2 测试程序设计为了方便逐级厘清PHY 测试中的问题,本文根据以太网数据信号的流经途径,设计了两种类型的环回测试,内部环回和外部环回分别如图2和图3所示。

图2 GPHY 内部环回结构图

图3 GPHY 外部环回结构图

PHY 内部环回用以检查PHY 内部数据流是否正常。期望的正常情况是 RXD[7:0]上的信号与TXD[7:0]上的信号相同,只是存在一段短暂时间上的滞后。在测试程序内部,逻辑应这样设计:数据发送后,比较接收数据缓冲区与发送数据缓冲区之间的数据差异,即可判断该项测试是否通过。若数据相同,则符合预期,测试通过;否则,测试未通过,这时系统会通过串口打印出数据差异的所在位置和错误提示信息。在PC 机上,开发人员根据这些日志,便可迅速定位问题。

在进行外部环回测试前,需要在RJ-45 上插入一个特制的水晶头。该水晶头的差分信号线要按照图3所示,把对应的差分信号线进行互连,水晶头插入RJ-45 后,就实现外部环回测试所需的信号连接。外部环回与内部环回的测试程序是一致的,差异点仅在于:外部环回模式要把GPHY 的0地址寄存器中的bit14 清零,以解除内部环回模式。

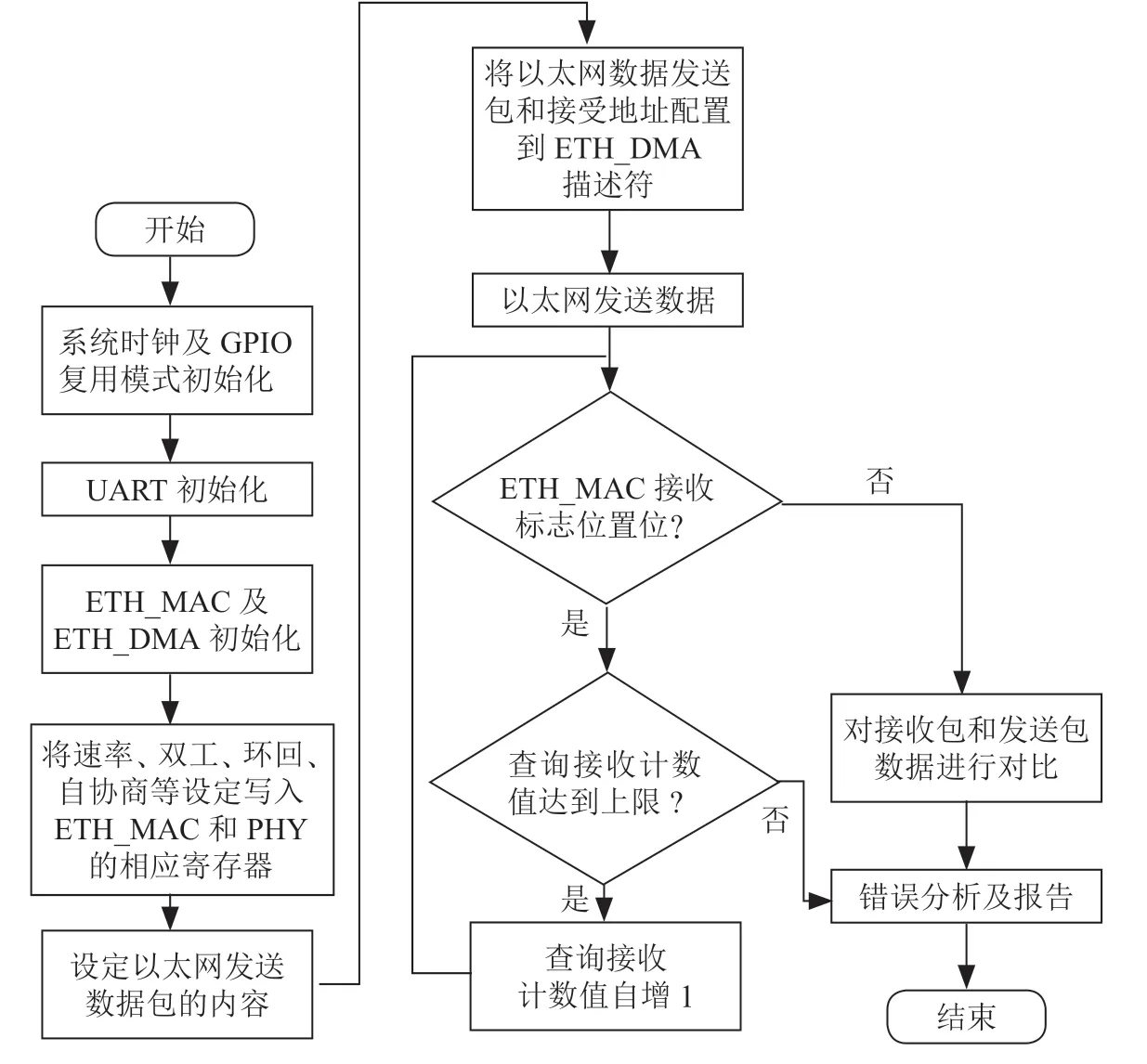

环回测试的流程如图4所示,其主要完成了如下6 项内容。

图4 环回测试流程图

(1)设定系统时钟,给APB 总线上的ETH 模块提供125 MHz 的PLLCLK。

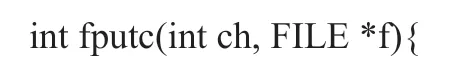

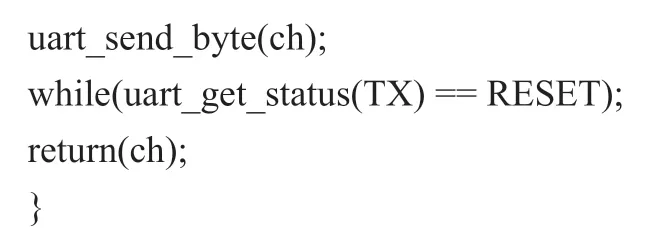

(2)UART 初始化,将UART 速率配置为“115 200 bps,8 bit,无校验位”格式。通过重定义标准库中的fputc实现对printf 函数的重定向,从而在日志中使用printf 格式化运行过程中变量,如寄存器的值、错误类型等,重定向的实现代码如下所示:

在调试阶段,我们期望尽可能详细地观察程序运行过程中的状态,而调试完成后,只想看关键的运行结果,忽略调试阶段加入的日志。为了实现这一目的,通过如下所示的宏函数来输出系统日志,便可动态地调整的日志等级。例如,当调试完毕后,进行循环的压力测试时,可以把宏函数LOG()中的“level>=DBG”修改为,“level>=INFO”,那么调试阶段所加入的DBG 等级的日志便不会输出。

(3)为了测试不同速率(10M-Base/100M-Base/1000MBase)、双工/ 半双工(Full/Half Duplex)、环回/ 非环回(Loopback/Non-Loopback)、是否自协商 (Auto-Negotiation)等模式的组合情况,我们设计了统一的多参数函数,来对PHY 寄存器的设定内容进行封装,函数声明如下所示:

int PHY_TEST(int rate, bool duplex, bool loopback, bool Auto-Neg);

PHY 寄存器的读写依赖SMI 接口,我们封装了读写操作的API,其声明如下:

unsigned short SMI_Read(unsigned short Address);

void SMI_Write(unsigned short Address, unsigned short Data);

因为IEEE802.3 规定的PHY 寄存器的地址和数据宽度都是16 比特,故采用unsigned short(无符号半字)类型作为形参和返回值的类型。SMI_Read()用于查询PHY 的状态标志位,如Link 状态、速度模式、自动交叉线等。SMI_Write()用于把PHY_TEST()传入的形参写入到PHY 的寄存器对应的比特位。

(4)在设定以太网发送数据包时,我们把源地址和目标地址固定下来,数据段长度设定为最大1 500,类型为ARP 数据包,除了地址和包长度之外,其他数据使用rand()生成的伪随机数来填充,这样随机化的数据让测试更接近真实使用PHY 时的情况。

(5)为实现对ETH_DMA 接收和发送描述符的设定,编写了如下的API:

void ETH_DMA_Desc(void *TxBuf, int TxSize, void*RxBuf, int RxSize);

ETH 发送数据时,ETH_DMA 从地址TxBuf 处搬移数据到GMII_TXD[7:0];ETH 接收数据时,ETH_DMA 从GMII_RXD[7:0]搬移数据到RxBuf。

(6)查询ETH_MAC 的接收标志位,若没有置位则循环查询,当循环的累积的次数超过了设定的上限,说明没有接收到数据,使用如下语句输出错误日志:

LOG(ERR,“ Receive polling timeout”);

若查询到ETH_MAC 的接收标志置为1 时,表示接收到了有效数据,并且接收已完成,这时通过对比接收到的数据包内容与发送时的数据包内容,如相同,则表明PHY 功能正常;如不同,则用如下语句输出错误日志:

LOG(ERR, “Index:%u, Expect: %u,Real:%u”, i,TxBuf[i], RxBuf[i]);

为了检验GPHY 稳定性,在main 函数内,循环调用PHY_TEST(),内部环回和外部环回测试若都能通过,即可证明GPHY 功能正常。GPHY 的功能有保障后,再移植TCP/IP 协议栈LwIP,不需要操作系统,即可实现ping 命令测试、TCP-Server 等功能。

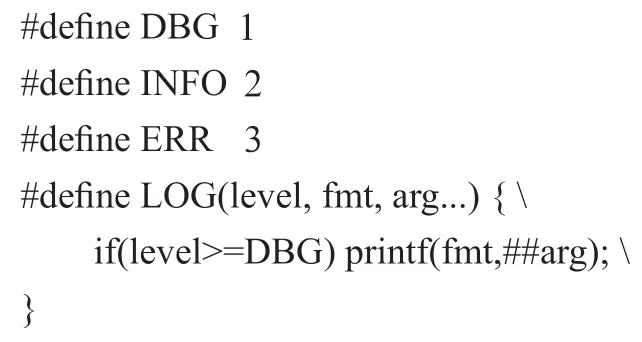

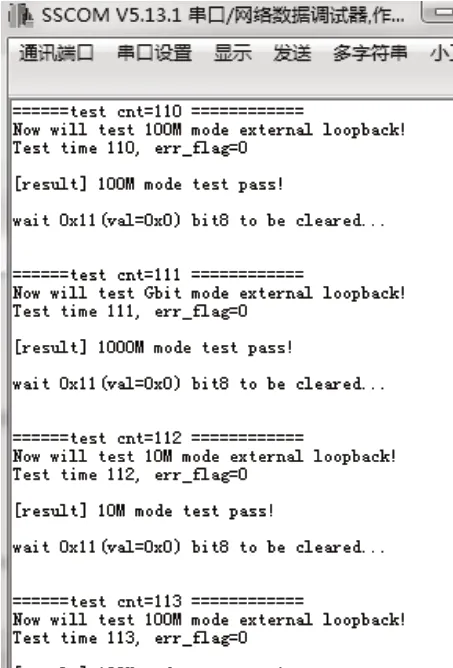

3 测试结果内部环回和外部环回的测试结果如图5、图6所示,图中展示的是压力测试过程中的系统日志,cnt 表示测试的计数,每循环调用一次PHY_TEST();[result]后的内容表示测试的结果,fail 或pass。

图5 内部环回测试结果

图6 外部环回测试结果

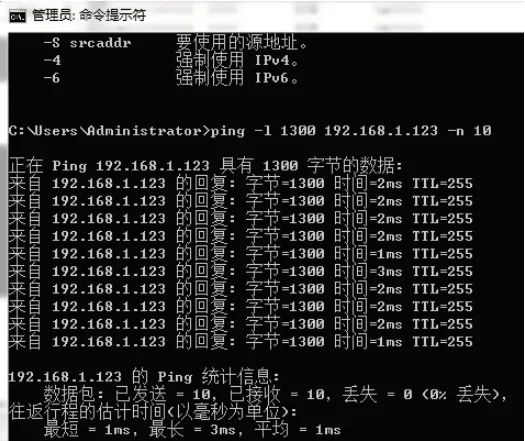

环回测试完成后,确保了PHY 可工作正常,通过LwIP协议栈,可以实现MCU 作为TCP Server,在window 的命令行中,用ping 来测试PC 机与MCU 之间的网络通路,实验结果如图7所示。

图7 ping 测试结果

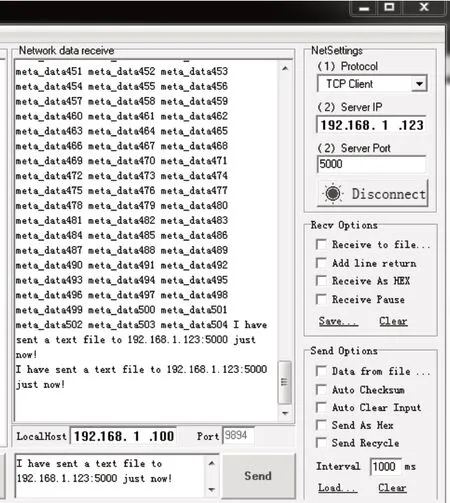

同时借助网络调试助手,在PC 机上通过TCP Client 协议,连接上作为TCP Server 的MCU,我们在MCU 的应用程序里设计Server 将收到的数据,再发送回给client,实验结果如图8所示。

图8 TCP-Server 测试结果

4 结 论本文介绍了千兆以太网物理层收发器测试系统的架构,提出了根据数据流分阶段对GPHY 进行环回测试的方法,阐述了环回测试程序的设计和实现,其中设计的可分级调整的日志系统与统一的测试函数接口,方便了多轮循环压力测试。最后,展示的两种环回测试的日志和基于LwIP 的ping与TCP-Server 测试结果,表明本文提出的测试方法科学有效,有利于快速定位问题,代码易于复用,同时可以为其他PHY 测试工作提供参考。