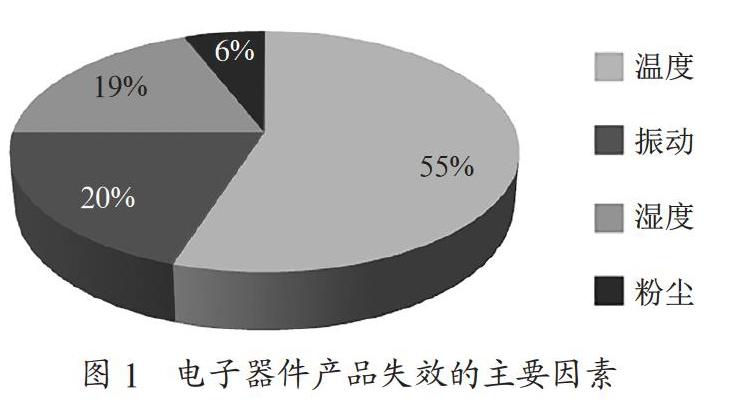

摘 要:文章基于GaAs pHEMT晶圆工艺现状,根据不同材料特性,从芯片设计、晶圆制程控制、封装材料选择三个维度进行了研究,报告了针对类似材料组合相对复杂的化合物半导体工艺器件在高加速温湿度应力(HAST)能力方面所面临的现状。同时,通过典型案例分析,说明了此类化合物器件在耐湿热能力设计及制程控制上需要注意的关键点,用于类似芯片设计或工艺开发工作进行参考。

关键词:化合物半导体;砷化镓;pHEMT;HAST;耐湿热能力

中图分类号:TN386 文献标识码:A 文章编号:2096-4706(2024)08-0079-05

DOI:10.19850/j.cnki.2096-4706.2024.08.018

0 引 言

基于JESD22-A110E.01定义,高加速温湿度应力测试(HAST)主要通过施加高温,高湿及偏压来加速湿气通过外部保护材料(密封剂或密封壳),或者外部保护材料和金属导体之间的粘结界面,来评估非气密性封装固体器件在潮湿环境中的可靠性[1]。

根据化学组成分类,常用的半导体材料可分为元素半导体、化合物半导体两大类。在化合物半导体中,有机化合物半导体虽然种类不少,但至今仍处于研究探索阶段。随着分子束外延(MBE)、金属有机物化学汽相淀积技术(MOCVD)和晶圆制程加工技术的发展和进步,早期主要用于军事领域(包括智能武器、雷达、通信等方面)的GaAs、InP、GaN等无机化合物半导体材料逐渐扩展到了民用电子领域,由于其具有电子迁移率较高[2]、禁带宽度宽、工作温度范围大、微波传输性能好等优点,近几年发展十分迅速。

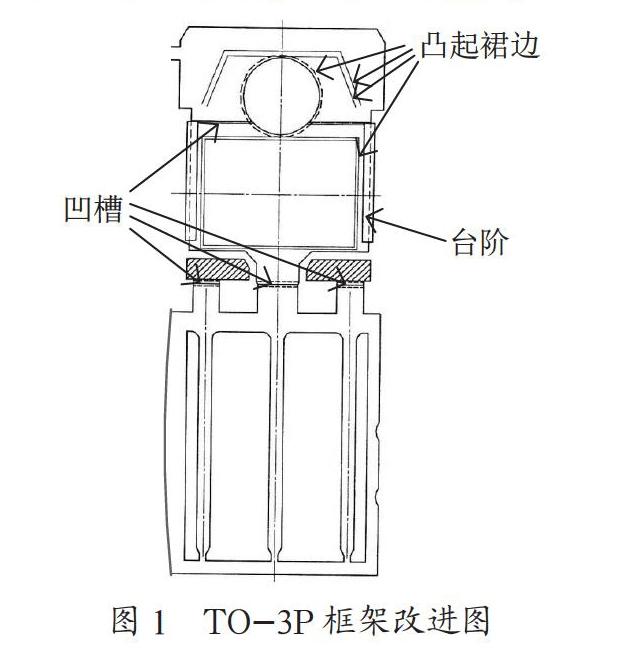

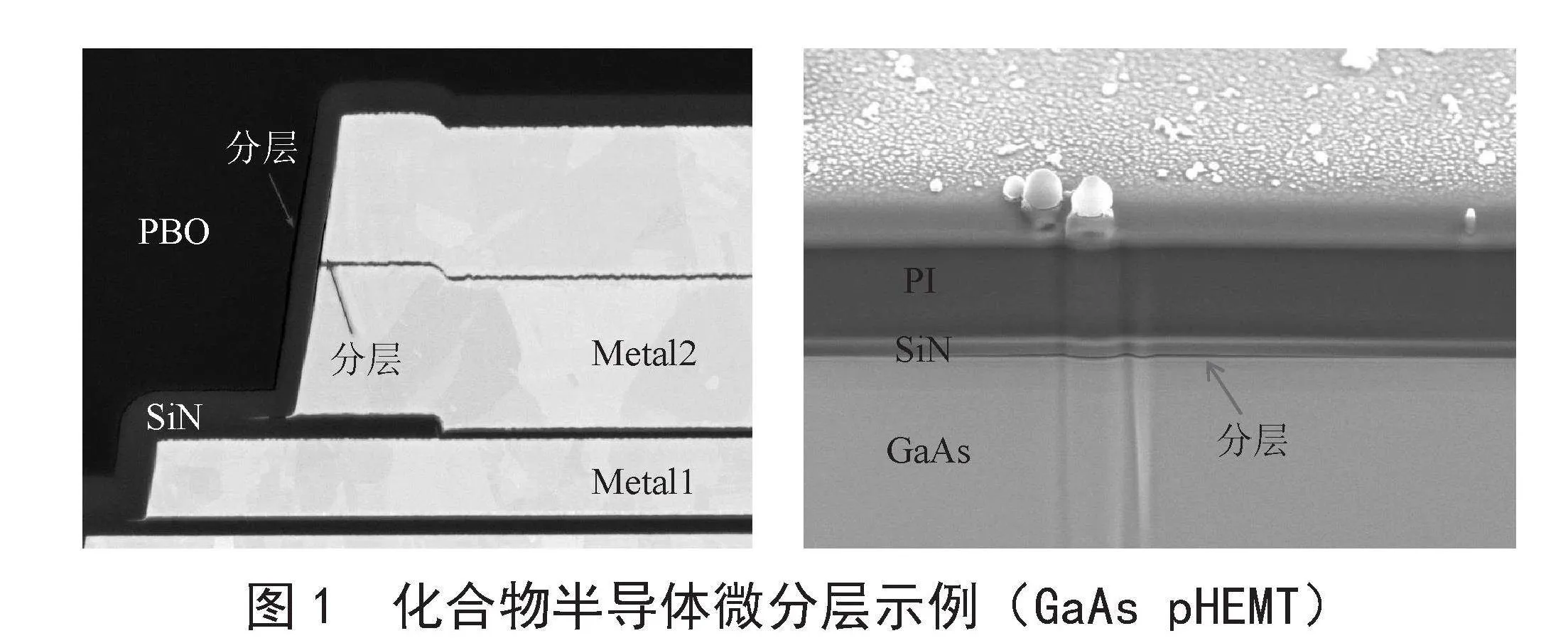

相较于第一代Si,Ge等元素半导体的CMOS,BJT等制造工艺,GaAs、InP、GaN等无机化合物半导体也发展出了多种不同工艺,如GaAs常用的pHEMT、HBT等工艺,此类工艺相较于传统的元素半导体制程(如硅基SOI工艺),虽然不太追求先进的工艺节点,但是在使用的材料组合上会更多样。例如GaAs pHEMT/HBT工艺在不同金属走线层间(如Metal1和Metal2之间)会有一道整平工艺,通过涂布有机聚合物材料如聚酰亚胺(PI)进行层间平坦化处理;为进一步提升可靠性,部分工艺还会在晶圆表面的钝化层上再涂布一定厚度的聚酰亚胺(PI)或聚苯并恶唑(PBO)保护层。由于PI、PBO类似热固性高聚物相较于传统的无机非金属材料(如SiO2、Si3N4等)在化学及物理特性上有较大差异,除了本身更易吸湿外,特别是在高温(如240 ℃)条件下进行固化,不同材料间的由于热膨胀系数(CTE)不同导致的热应力匹配也将更为复杂、更难控制,因此,此类芯片内部也更容易出现微观结构上的分层,如图1所示。

针对此现状,为提高此类化合物半导体器件的耐湿热能力,在设计上需要尽量考虑到产品耐湿热应力设计冗余度;晶圆制程则主要从材料选择,降低各制程应力,增加层间粘附性等大方向上进行控制;而针对封装制程,在材料的选择及匹配性上,要求也会更高。

本文以GaAspHEMT工艺为例,分别从前述三方面进行举例浅析。

1 设计上提高产品耐湿热能力冗余度

1.1 提高金属走线或者器件之间电气绝缘能力

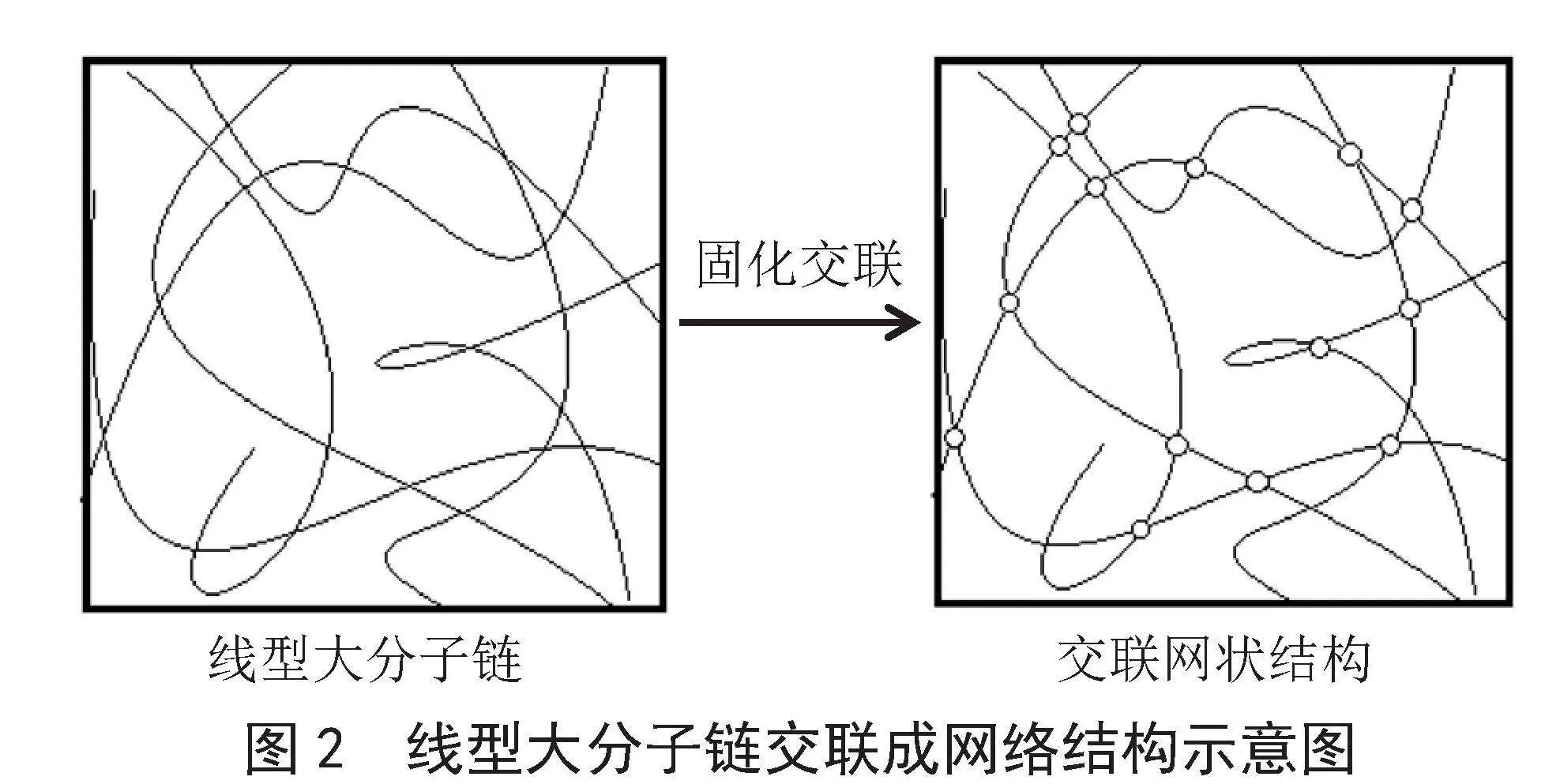

以GaAs pHEMT工艺为例,在业内常用聚酰亚胺(PI)这类高聚物作为不同金属层间介质进行填充或整平,基于热固性高聚物交联网状的结构特点(具体如图2所示),其相较于无机非金属材料在分子结构的致密度、耐电化学稳定性及耐候性方面能力较弱,易被潮气或者有机溶剂等化学药品所侵蚀。特别是在湿热老化环境中,聚酰亚胺的电绝缘性能会出现较为明显的变化[3]。

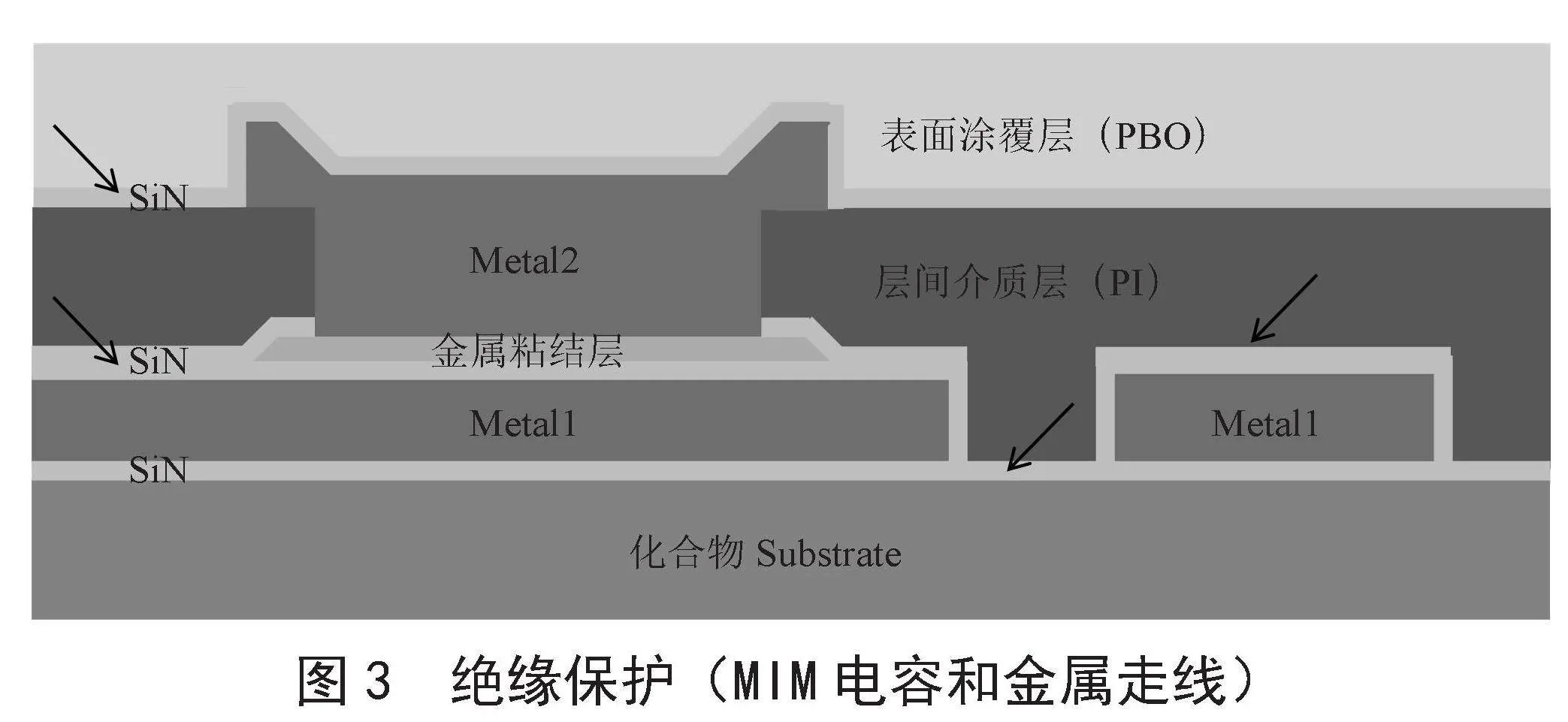

器件或者导线直接暴露在此种材料环境中,在长期的电、湿、热、残余化学离子的影响下,可靠性相对来说更容易劣化。如主动器件(Gate-Source/Drain)、不同金属导线之间由于电压差而发生的水平或者垂直方向离子(电)迁移问题[4]。所以在器件或导线之间的绝缘设计上,应尽量选择使用氮化硅类似具有高致密高绝缘特性的无机非金属材料进行绝缘保护,以提高芯片的耐湿热能力。如图3所示,针对MIM(Metal-Insulator-Metal)电容和导线上均覆盖了氮化硅进行保护。其中,图示MIM电容“金属粘结层”设计可提高器件的耐湿热以及电容边缘耐介质击穿能力。

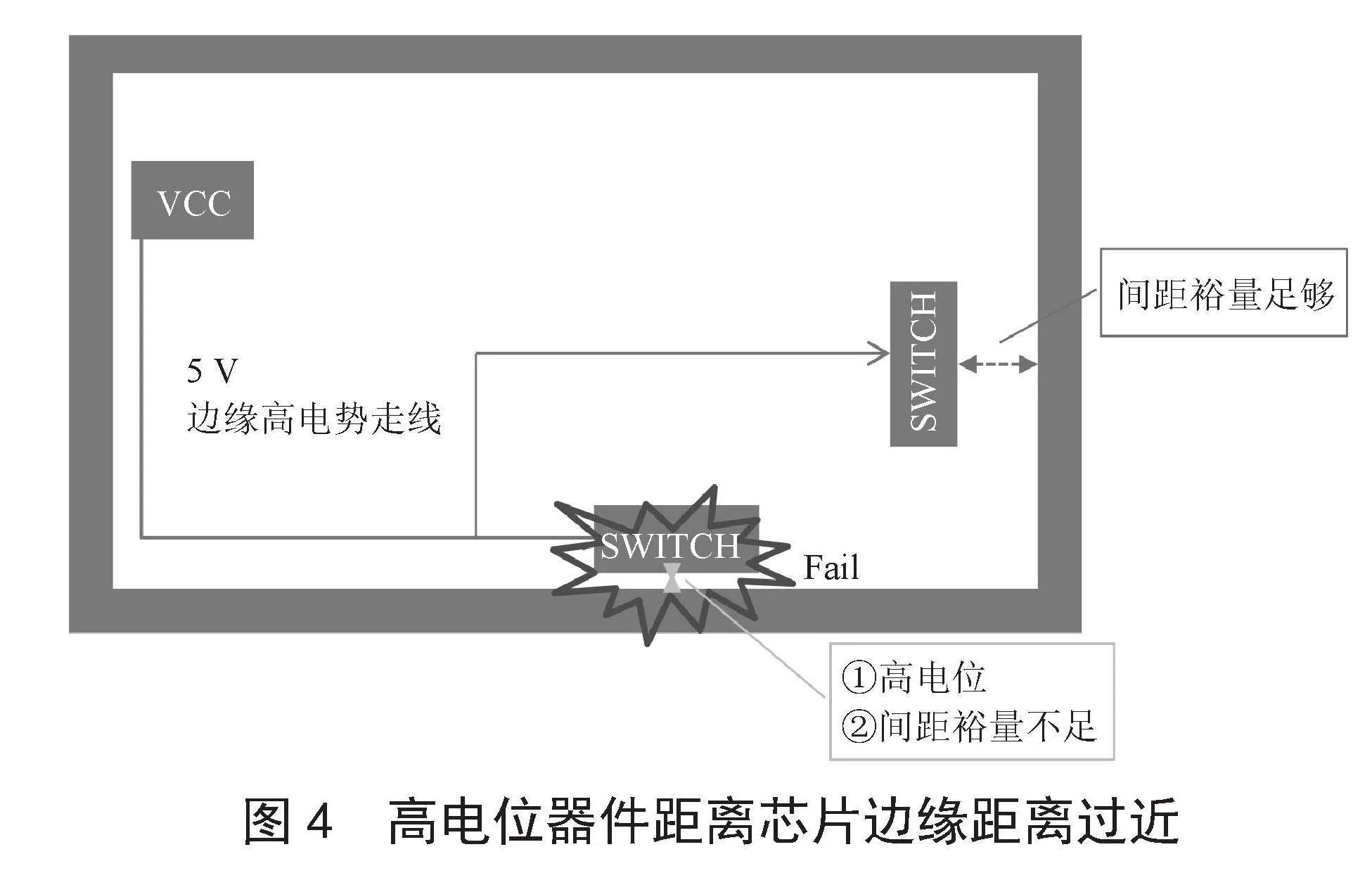

1.2 避免芯片边缘高电位走线及器件设计

从芯片结构和加工制程特点来讲,芯片边缘为整颗产品耐湿热能力薄弱区域,在设计上需要尽量避免边缘高电位走线或者高电位器件设计。

如图4所示,由于器件边缘存在5 V高电位走线及有源器件设计,导致图示底部近边缘(6 μm)的有源器件位置(SWITCH)在电应力的作用下容易出现高比例的湿热失效问题;而右侧SWITCH位置由于留有足够的边缘间距裕量(15 μm),则很安全。对此,作为晶圆厂,在开发对应晶圆工艺时,需要评估出自身工艺在不同电应力下的耐湿热能力,找出“电应力+边缘间距裕量”的安全规则,以更好的指导芯片设计。而作为设计师,在设计产品时也需要有意识去尽量避免芯片边缘高电位走线或者器件设计,留足可靠性设计冗余度。

2 晶圆制程工艺控制

2.1 提高层间粘附性

提高层间粘附性的主要目的是平衡不同材料间由于热膨胀系数不同产生的热应力匹配以及制程应力的影响。由于GaAs基底很容易氧化,因此,在GaAs基底上沉积第一层氮化硅保护膜之前(部分晶圆厂称之为passivation layer或first silicon nitride),选择适宜的清洗方式非常重要。例如,将GaAs基底先放入酸溶液中进行清洗,再向经过清洗的GaAs基底表面通入流动的氨气,并使氨气进行等离子反应,以去除GaAs基底表面的氧化物,从而提高与第一层氮化硅保护膜之间的粘附性[5]。

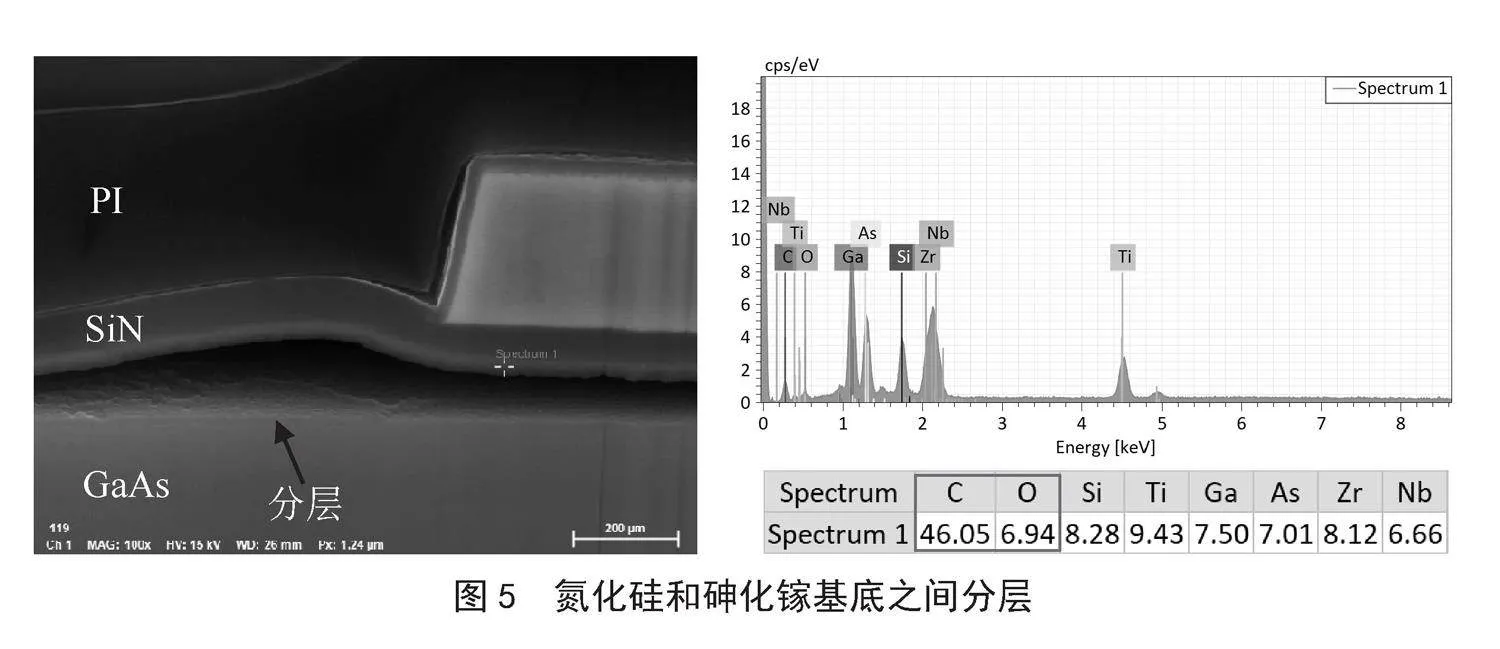

如图5所示器件,基于此器件对应晶圆制程的设备能力及工艺特点,针对有源器件完成后沉积第一层氮化硅前,初期工艺流程为:先进行有机清洗(N-甲基吡咯烷酮),然后再Descum。由于GaAs基底本身比较容易氧化,在Descum氧等离子体的物理轰击下,很容易形成无机氧化层,从而影响了GaAs基底和介质层间的粘附性,造成氮化硅和GaAs基底间出现分层问题。后来将氮化硅沉积前工序调整为“Descum+碱洗(氨水)”的组合方式后,此位置的分层现象得到了明显改善,大大提升了此器件在电应力下的耐湿热能力。

2.2 应力控制

在晶圆工艺控制上,除了通过优化工艺中的真空度、温度、反应气体流量比、功率、时间等参数,得到应力较低的氮化硅薄膜[6]。在材料的选择上,也需要考虑到各种材料的热应力匹配,并基于材料特性,尽量降低对应工艺过程可能产生的内应力。

如前述图1所示GaAs pHEMT工艺案例,基于晶圆制程前后翘曲度绝对差值分析,应力占比最大的为最外层聚苯并恶唑(PBO)涂覆层,此点主要与此层材料本身特性(热固型高聚物)以及厚度较厚(5~

6 μm)有关。由于此类材料常规的固化温度相对较高,传统配方甚至需要在350 ℃的条件下固化数小时,为降低此工序引入的热/固化应力的影响,可通过变频微波辐射(VFM)处理后,将固化温度降到200 ℃ [7],或者直接选择具有低温固化特性的配方,如HD MicroSystems的HD-8930,在200 ℃的条件下就能直接实现固化。

3 封装材料选择

3.1 银浆选择

导电银浆主要由具有导电及散热作用的银粉,提供力学性能及粘结性的有机组分组成。其中,有机组分主要有基体树脂、固化剂、固化促进剂、稀释剂等[8]。为了说明银浆对化合物半导体器件的耐湿热能力影响,选取了两款高导热烧结银浆进行对比分析。

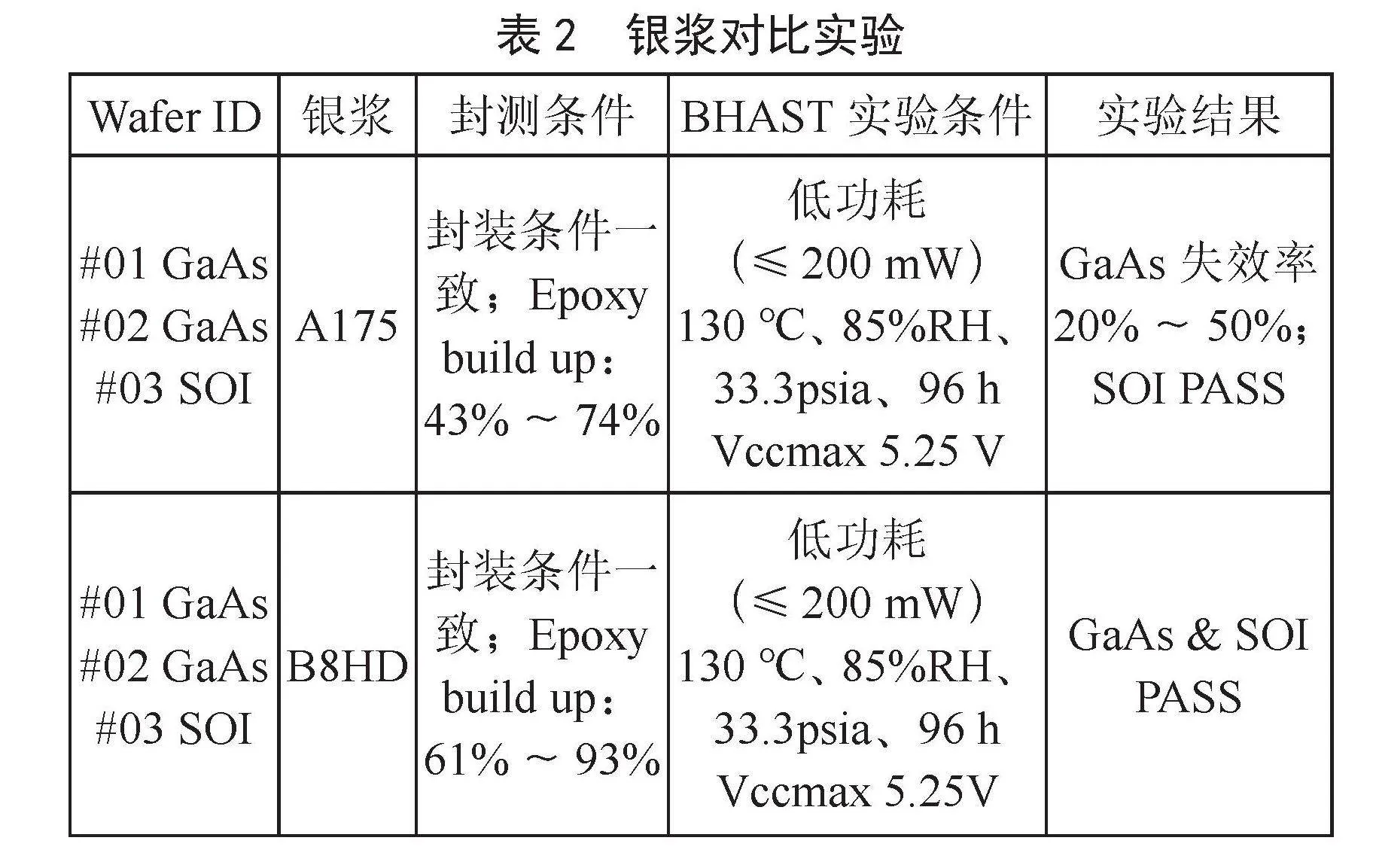

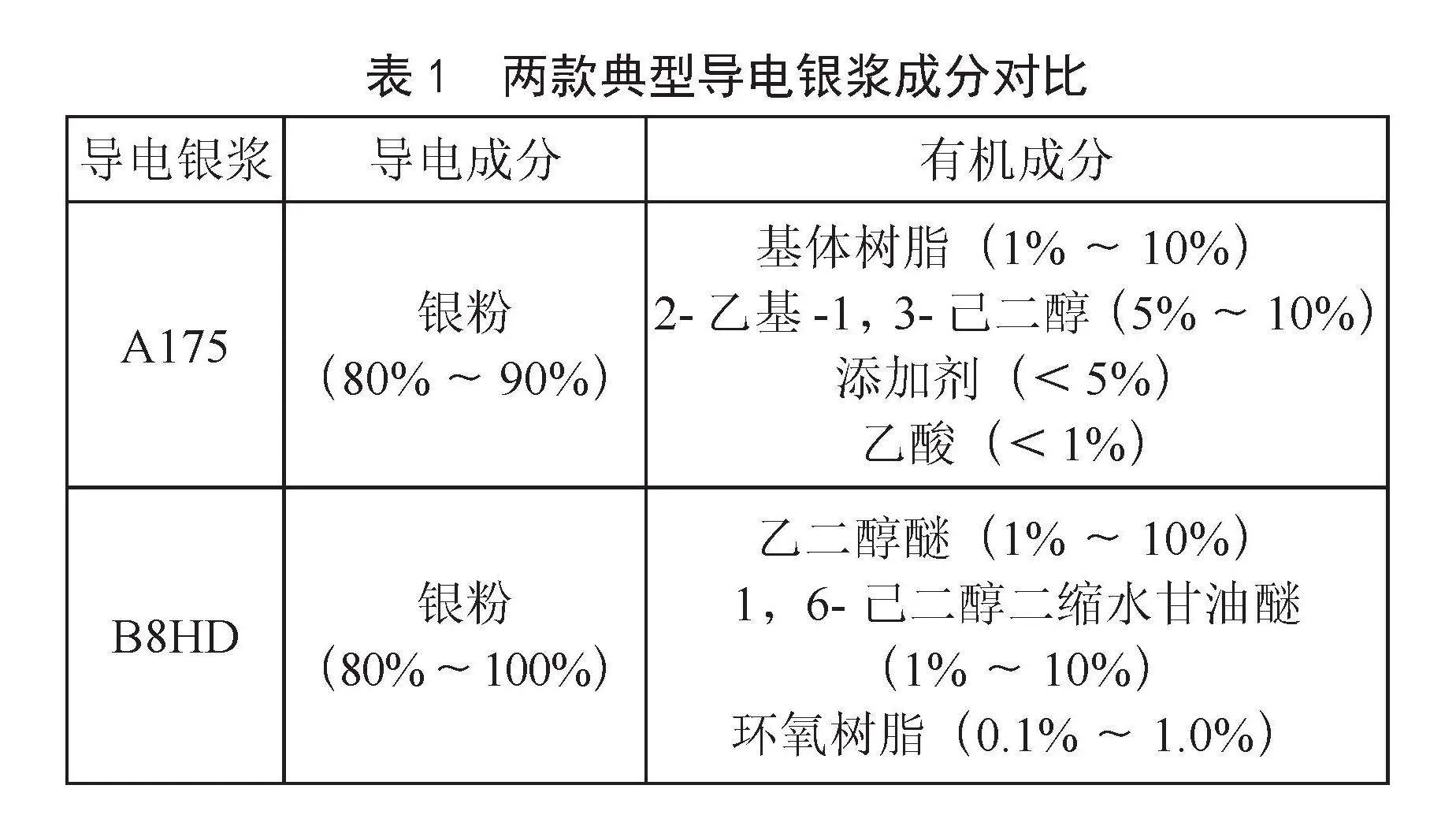

如表1所示,从银浆技术资料上提供的信息,导电银浆A175主要组分包括银粉、基体树脂、2-乙基-1,3-己二醇、添加剂及乙酸;导电银浆B8HD主要组分包括银粉、乙二醇醚、1,6-己二醇二缩水甘油醚及环氧树脂。

针对上述两种银浆,安排了平行对比实验(实验结果如表2所示;样品示例如图6所示,内含两颗GaAs和一颗SOI芯片),进行的多组验证结果均显示,使用导电银浆A175,两颗GaAs芯片均出现不同比例的HAST失效,SOI芯片无异常;而导电银浆B8HD表现很稳定,GaAs和SOI芯片均没有异常。(说明:本案例已通过失效分析(FA)、银胶爬胶高度对比分析,排除了由于银浆中银离子迁移导致的失效模式,在此不做展开)。

基于技术资料上提供的银浆成分进行初步分析,银浆配方A175含有少量乙酸(CH3COOH),这在业内较少使用,有专利上表述乙酸的主要目的是为了去除银粉上附着的杂质,并起到促进烧结的作用。由于乙酸分子间具有氢键,较强的作用力不利于挥发,无法保证能在上芯(Die bond)过程中充分释放;同时,乙酸水溶液呈弱酸性且腐蚀性强,特别是对金属有强烈的腐蚀性,HAST实验高温高湿及偏压的环境更利于加速这种作用,所以整体上来讲,其作为配方组分的选择上并不是很友好。叠加化合物半导体芯片内部微观结构无法做到SOI工艺那么致密及绝缘,因此,此类银浆配方用在化合物半导体上并不太合适。不足的是,由于实验手段有限,本案例目前仅基于试验结果从银浆配方组分上进行了初步分析,期待有专业人士能针对失效机理做进一步研究论证。

此案例说明,针对类似GaAs pHEMT工艺生产的化合物半导体,为保证器件在电应力下的耐湿热能力,在银浆的选择上,需要比SOI工艺更为谨慎。

3.2 环氧塑封料的选择

针对非气密性半导体器件,业内主要使用环氧塑封料(Epoxy Molding Compound, EMC)进行封装,此材料主要由环氧树脂、较高比例填料、固化剂和各种添加剂组成。

由于塑封料本体所含的环氧树脂为高分子材料结构,导致其处于潮湿环境中容易吸收水分,水气可通过塑封料本体以及塑封料与基板或者框架之间的粘合界面进入封装体,不仅削弱了塑封料与框架或者基板之间的粘接力,且水气中携带的杂质或者离子还会引起电子线路的腐蚀,甚至侵入芯片内部,最终导致电路故障或者器件失效等问题。

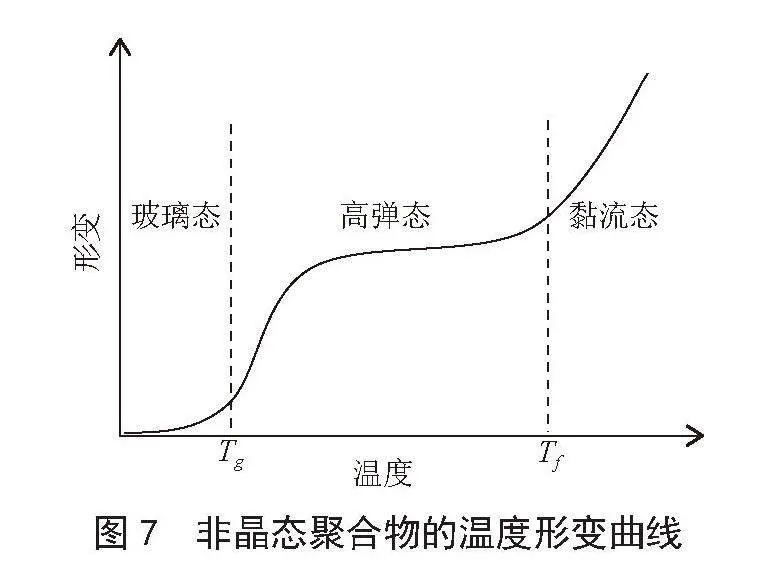

高温也是引起半导体器件在恶劣环境中失效的主要加速因素。特别是塑封料与芯片、金属引线框架或者基板之间的热膨胀系数(CTE)不匹配而产生的热应力,对器件的可靠性影响十分显著。当温度升高到环氧树脂的玻璃化温度(Tg)时,环氧树脂由较硬的璃态转变为高弹态(如图7所示)[9],其热膨胀系数由小变大,与芯片、引线框架或者基板的热膨胀系数不匹配度增大,从而引起器件内部出现热应力变形。与此同时,塑封料的储能模量也会急剧变小,抵抗变形的能力降低,更易导致封装分层,从而加剧外部环境湿气及污染离子的侵入[10]。

目前业内针对GaAs类非气密性封装器件的潮敏等级要求一般是≤MSL3,但鉴于此类化合物芯片从材料组分及工艺制程能力来讲,其耐湿热能力相较于SOI工艺会更弱,因此,为更好的保证器件在电应力下的耐湿热能力,此类器件在塑封料的选择上,应优先选择粘结性好、热膨胀系数小、玻璃化温度较高、且吸湿性更低的塑封料。

4 结 论

本文基于GaAs pHEMT工艺现状,从芯片设计、晶圆制程控制、封装封料选择三个维度进行了分析,以此说明如何从这三个方面提高相似工艺器件的耐湿热能力。

随着半导体技术的发展,目前业内用于微波毫米波、射频或功率器件的化合物半导体材料应用越来越广泛,类似GaAs HBT、GaAs pHEMT/HBT等,只要在材料组合及工艺上与文中所述GaAs pHEMT案例有相似性,在耐湿热能力上均会面临相同的问题,因此在器件的设计开发时均需要格外注意。

同时,限于实验手段有限,文中部分失效机理并未进行深入研究,其中观点愿与业内专业人士商榷,不足之处也期待能得到指正。

参考文献:

[1] JEDEC. HIGHLY ACCELERATED TEMPERATURE AND HUMIDITY STRESS TEST(HAST):22-A110E.01 [S/OL].[2023-06-25].https://www.jedec.org/document_search?search_api_views_fulltext=22-A110E.01.amp;order=titleamp;sort=asc.

[2] 许俊焯,蒙自明.高电子迁移率晶体管的研究进展 [J].科技创新与应用,2023,13(13):99-104.

[3] 陶君.聚酰亚胺薄膜湿热老化性能研究 [J].工程塑料应用,2023,51(1):98-103.

[4] 许燕,黄云,邓文基.GaAs PHEMT器件的失效模式及机理 [J].电子产品可靠性与环境试验,2007(6):19-22.

[5] 于良成,白龙刚,杨国文,等.砷化镓基半导体器件的制造方法:CN112233970B [P].2023-03-23.

[6] 王敬轩,商庆杰,杨志.低压化学气相淀积低应力氮化硅工艺研究 [J].电子与封装,2021,21(8):97-101.

[7] 王涛,李金辉,赵雅绪,等.光敏聚苯并恶唑的研究现状与发展趋势 [J].材料导报,2020,34(19):19183-19189.

[8] 王林.微电子工业用银浆导电填料的制备研究 [D].成都:电子科技大学,2015.

[9] 何曼君,张红东,陈维孝,等.高分子物理:第3版 [M].上海:复旦大学出版社,2021:106.

[10] 王良超.半导体器件用环氧塑封料的性能研究 [D].西安:西安电子科技大学,2020.

作者简介:黄琴琴(1985—),女,汉族,四川德阳

人,中级工程师,本科,主要研究方向:半导体元器件工艺及技术。

收稿日期:2023-09-10

Research on Current Situation of Temperature and Humidity Highly Accelerated Stress Test (HAST) Capability of Compound Semiconductors

HUANG Qinqin, SHI Jun

(Chengdu Ganide Technology Co., Ltd., Chengdu 610016, China)

Abstract: Based on the current situation of GaAs pHEMT wafer process, this paper studies from three dimensions: chip design, wafer process control, and packaging material selection according to different material characteristics. It reports the current situation faced by compound semiconductors with relatively complex material combinations in terms of temperature and humidity Highly Accelerated Stress Test (HAST) capabilities. Through typical case analysis, the key points that such compound semiconductors need to pay attention to in the design and process control are explained, which can be used for reference in similar chip design or process development work.

Keywords: compound semiconductor; GaAs; pHEMT; HAST; temperature and humidity stress test capability