摘" 要:在异步串行通信中,由于串行接口硬件设备的工作频率限制,以及信号跳变引起的抖动、环境干扰等影响,采用传统方法实现异步串行通信的通信接口无法可靠地完成高速率通信。文章采用VHDL语言,设计一种基于奈奎斯特的异步串行通信接口,包括数据接收、数据发送和2倍波特率的采样时钟三个模块。ISE和ModelSim联合仿真与实际工程的验证表明,使用新方法设计的接口在5 Mbit/s的高速率下,系统可稳定、可靠地与外部设备进行数字通信。

关键词:奈奎斯特采样;FPGA;VHDL;异步串行通信

中图分类号:TN911.72" 文献标识码:A" 文章编号:2096-4706(2024)09-0024-06

Design of FPGA Asynchronous Serial Communication Interface Based on Nyquist Sampling

CHEN Wei1,2, PU Hongping1,2, YANG Shiyong1,2, ZHANG Shuhui1,2

(1.School of Automation and Information Engineering, Sichuan University of Science amp; Engineering, Yibin" 644000, China; 2.Artificial Intelligence Key Laboratory of Sichuan Province, Yibin" 643000, China)

Abstract: In asynchronous serial communication, due to the frequency limitations of serial interface hardware devices, as well as the effects of signal jitter and environmental interference caused by signal jumps, communication interface that it uses traditional methods for implementing asynchronous serial communication cannot reliably complete high-speed communication. It uses VHDL language to design an asynchronous serial communication interface based on Nyquist, which includes three modules: data reception, data transmission, and a sampling clock with a 2x baud rate. The joint simulation of ISE and ModelSim and practical engineering verification show that the interface designed using the new method can make system digital communicate with external devices stably and reliably at a high speed of 5 Mbit/s.

Keywords: Nyquist sampling; FPGA; VHDL; asynchronous serial communication

0" 引" 言

在工业界中,数字通信是控制信息和传递数据的主要传输手段。然而,随着现代电子工业的不断发展,工业控制、工业测量等系统经常需要接入众多的、不同种类的外部传感设备,这就导致系统接口的复杂程度不断提高。传输数据量的不断增长,对通信方式也有着更高的需求。

通常,外接设备与系统的通信方式采用异步串口进行数据传输[1]。通用异步收发器(Universal Asynchronous Receiver Transmitter, UART)是一种遵循异步串行通信协议的串行通信接口,具有传输线少、可靠性高、成本低、易实现等特点[2,3],因此被广泛地应用于农业、工业、军事等众多领域[4–6]。随着外接设备的日益丰富,外设与系统的数据传输也需要更高速率。针对这一需求,异步串行通信的传统方法常有:8倍、16倍、25倍波特率分频器[7–9]。通过对系统时钟进行分频,根据分频系数的奇偶性采用奇数分频或偶数分频,将分频系数作为数据采样时钟的节拍,并在采样时钟中间进行取数。然而,这些异步串行通信的传统方法已无法满足外设与系统之间的高速通信要求。为了满足高速通信这一需求,需要解决高速异步串行通信的数据可靠传输这一难题。

因此,本文首先针对16倍波特率分频器的传统方法进行理论分析与研究,再通过对奈奎斯特采样进行理论分析,提出设计一种基于奈奎斯特采样的FPGA异步串行通信接口。

1" UART通信原理

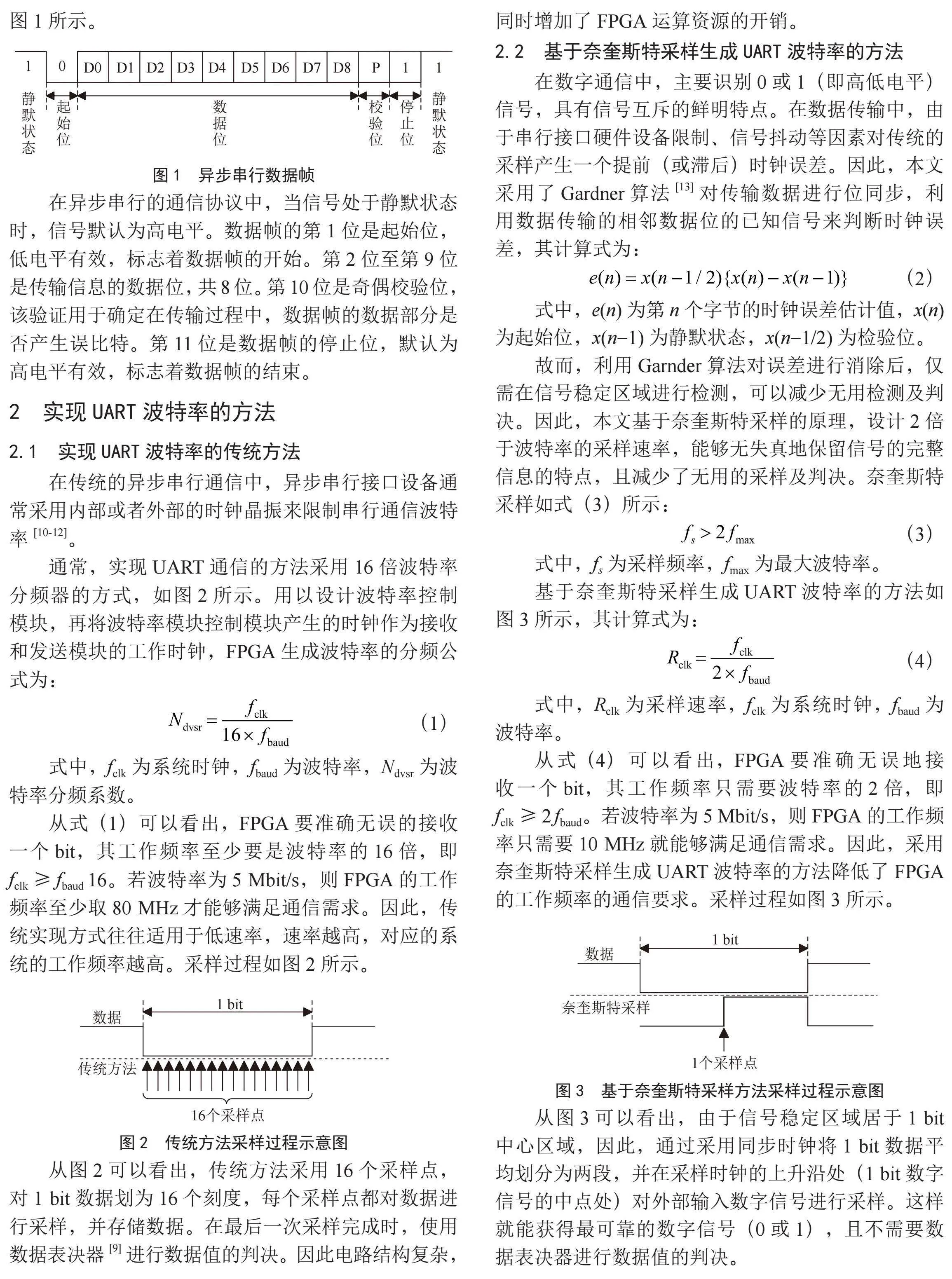

在串口通信中,异步串行通信方式是以字符为单位进行传输,每个字符都可以作为独立的信息进行传输。每帧数据的各个比特时间间隔是相同,而相邻的两帧数据时间间隔是不固定的,可以随意设置。通信双方都必须保持相同的数据帧格式(即“起始位+数据位+校验位+停止位”)和波特率。具体格式如图1所示。

在异步串行的通信协议中,当信号处于静默状态时,信号默认为高电平。数据帧的第1位是起始位,低电平有效,标志着数据帧的开始。第2位至第9位是传输信息的数据位,共8位。第10位是奇偶校验位,该验证用于确定在传输过程中,数据帧的数据部分是否产生误比特。第11位是数据帧的停止位,默认为高电平有效,标志着数据帧的结束。

2" 实现UART波特率的方法

2.1" 实现UART波特率的传统方法

在传统的异步串行通信中,异步串行接口设备通常采用内部或者外部的时钟晶振来限制串行通信波特率[10-12]。

通常,实现UART通信的方法采用16倍波特率分频器的方式,如图2所示。用以设计波特率控制模块,再将波特率模块控制模块产生的时钟作为接收和发送模块的工作时钟,FPGA生成波特率的分频公式为:

式中,fclk为系统时钟,fbaud为波特率,Ndvsr为波特率分频系数。

从式(1)可以看出,FPGA要准确无误的接收一个bit,其工作频率至少要是波特率的16倍,即fclk≥fbaud 16。若波特率为5 Mbit/s,则FPGA的工作频率至少取80 MHz才能够满足通信需求。因此,传统实现方式往往适用于低速率,速率越高,对应的系统的工作频率越高。采样过程如图2所示。

从图2可以看出,传统方法采用16个采样点,对1 bit数据划为16个刻度,每个采样点都对数据进行采样,并存储数据。在最后一次采样完成时,使用数据表决器[9]进行数据值的判决。因此电路结构复杂,同时增加了FPGA运算资源的开销。

2.2" 基于奈奎斯特采样生成UART波特率的方法

在数字通信中,主要识别0或1(即高低电平)信号,具有信号互斥的鲜明特点。在数据传输中,由于串行接口硬件设备限制、信号抖动等因素对传统的采样产生一个提前(或滞后)时钟误差。因此,本文采用了Gardner算法[13]对传输数据进行位同步,利用数据传输的相邻数据位的已知信号来判断时钟误差,其计算式为:

式中,e(n)为第n个字节的时钟误差估计值,x(n)为起始位,x(n-1)为静默状态,x(n-1/2)为检验位。

故而,利用Garnder算法对误差进行消除后,仅需在信号稳定区域进行检测,可以减少无用检测及判决。因此,本文基于奈奎斯特采样的原理,设计2倍于波特率的采样速率,能够无失真地保留信号的完整信息的特点,且减少了无用的采样及判决。奈奎斯特采样如式(3)所示:

式中,fs为采样频率,fmax为最大波特率。

基于奈奎斯特采样生成UART波特率的方法如图3所示,其计算式为:

式中,Rclk为采样速率,fclk为系统时钟,fbaud为波特率。

从式(4)可以看出,FPGA要准确无误地接收一个bit,其工作频率只需要波特率的2倍,即fclk≥2 fbaud。若波特率为5 Mbit/s,则FPGA的工作频率只需要10 MHz就能够满足通信需求。因此,采用奈奎斯特采样生成UART波特率的方法降低了FPGA的工作频率的通信要求。采样过程如图3所示。

从图3可以看出,由于信号稳定区域居于1 bit中心区域,因此,通过采用同步时钟将1 bit数据平均划分为两段,并在采样时钟的上升沿处(1 bit数字信号的中点处)对外部输入数字信号进行采样。这样就能获得最可靠的数字信号(0或1),且不需要数据表决器进行数据值的判决。

与需对每个bit电平采样16次的传统实现方式相比,本文所提出的方式仅需在每个bit电平的中点处进行一次采样。这样既节省了FPGA的逻辑资源,又减少了无用检测及判决,还提高了系统的运行效率。

3" UART模块设计

UART模块主要由接收和发送模块组成,发送模块主要根据数据帧的格式,通过位移寄存器实现发送数据的并串转换,由低位到高位进行传输。接收模块主要通过接收位移寄存器对接收数据进行采样,实现数据的串并转换。

3.1" 接收模块

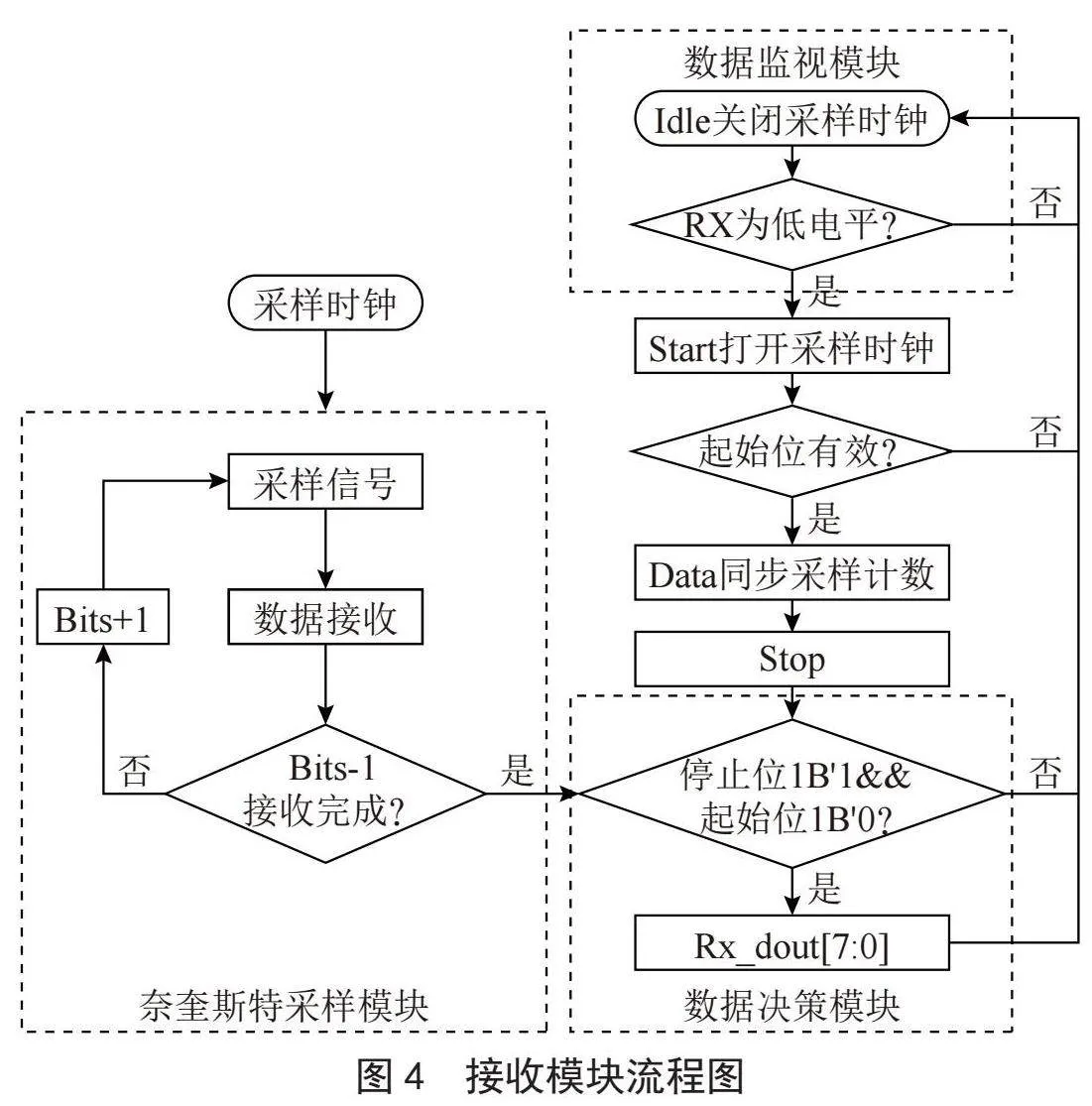

接收模块主要由数据监视模块、采样时钟、奈奎斯特采样模块和数据决策模块组成,如图4所示。

其中,数据监视模块主要实现对外部输入信号的数据进行监视。当RX为低电平输入时,首先采用Gardner算法对输入数据进行位同步,再开始产生采样时钟,接收模块开始运行,且实时判别数据有效性。若低电平不满足1 bit的持续时间,则判别为无效信号,并返回Idle状态,关闭采样时钟,且实时监测信号变化。反之,则判别为起始位有效,进入数据采集模块进行。

在数据采集模块中,FPGA生成奈奎斯特采样时钟,用以进行数据采样。同时,将接收数据进行串并转换,以及对数据进行同步采样计数,以确保FPGA状态与数据采样速率同步。

在接收数据进行串并转换后,由数据决策模块对接收数据进行有效性判定。其判决条件为同时对数据的起始位和停止位进行分别进行高低电平判别。若条件满足,则判定数据有效,更新当前接收到的数据,并返回Idle状态,等待下一次数据接收。若条件不满足,则判定数据无效,丢掉当前接收数据,并返回Idle状态,继续监测RX输入电平的状态。

3.2" 发送模块

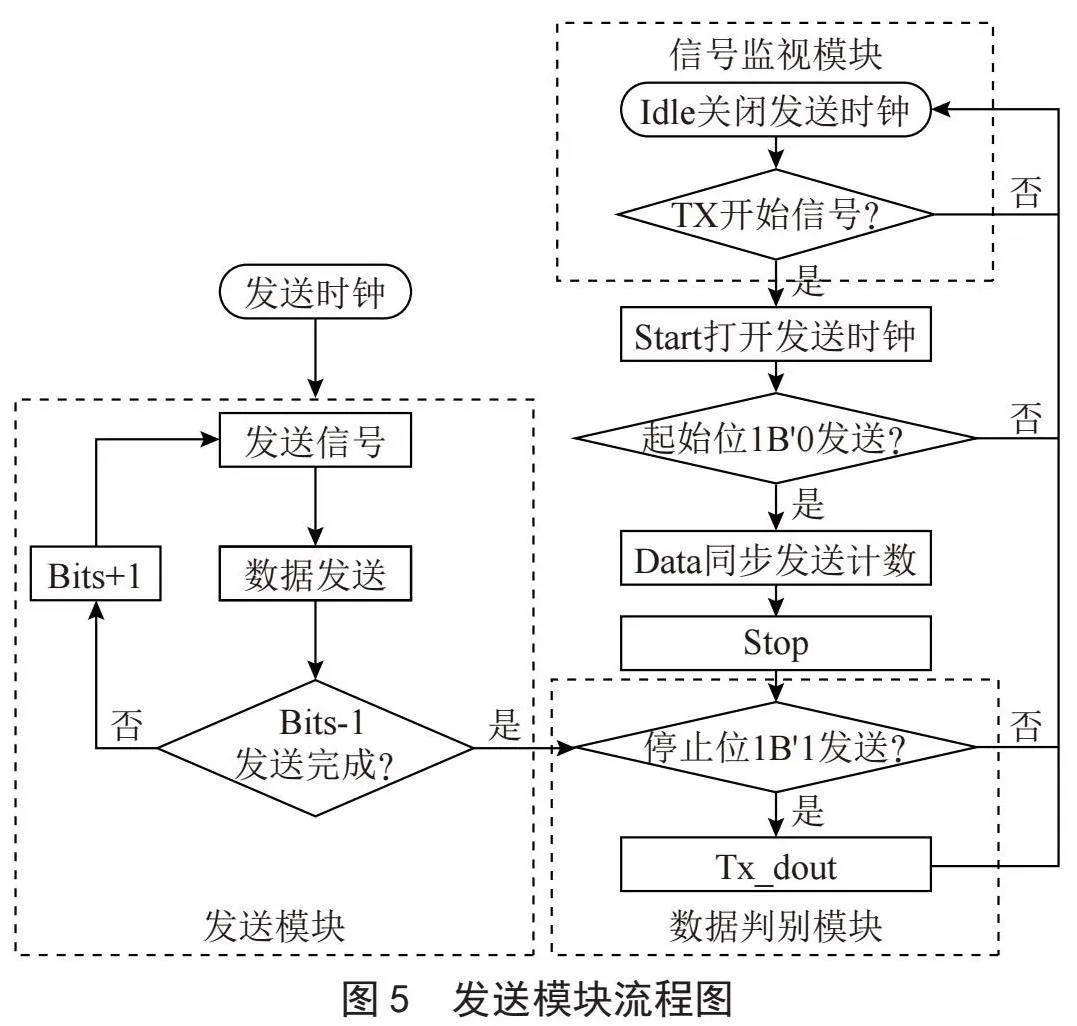

发送模块主要由信号监视模块、发送时钟、发送模块和数据判别模块组成,如图5所示。

其中,信号监视模块主要实现对TX开始信号进行监视。若TX信号输入为高电平时,开始产生发送时钟,发送模块开始运行。若TX信号输入为低电平时,则输出端口输出高电平。

在数据发送模块中,FPGA生成发送时钟,用以数据发送。同时,通过位移寄存器将发送数据进行并串转换。以及对数据进行同步发送计数,以确保FPGA状态与数据发送速率同步。

在发射模块对数据位发送后,发送模块对数据停止位进行发送,通过数据判断模块对发送数据进行停止位计数,若停止位满足1 bit的持续时间,则数据发送完成,返回Idle状态等待下一次数据发送。若停止位不满足1 bit的持续时间,则对数据的停止位继续计数。

4" 系统设计与仿真

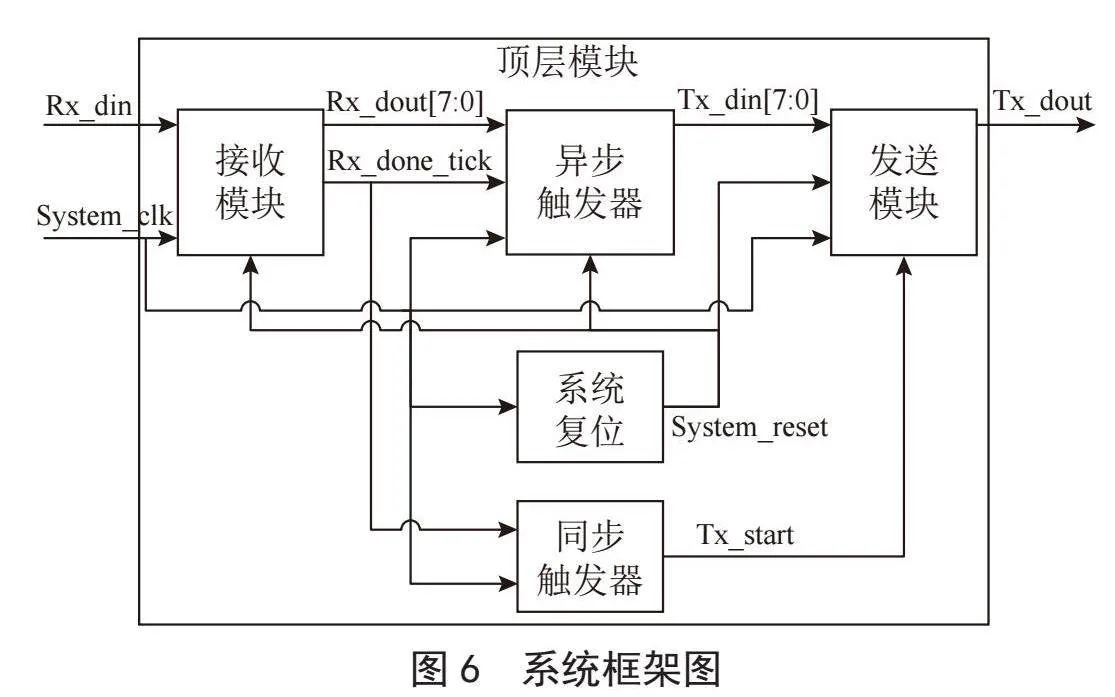

为验证UART接收和发送模块的功能,设计了一个UART系统,该系统主要由顶层模块、接收模块和发送模块组成。通过顶层模块将接收模块和发送模块联合组成一个完整的系统,其系统框架如图6如所示。

4.1" 系统仿真

为验证系统的功能,采用ModelSim仿真软件进行功能时序及功能验证。通过将Testbench的仿真数据作为UART的输入数据,而接收模块接收到的数据直接透传至发送模块,作为UART的输出数据,并发送。既可完成整个收发链路的时序和功能验证,又能在ModelSim软件里面进行代码调试。

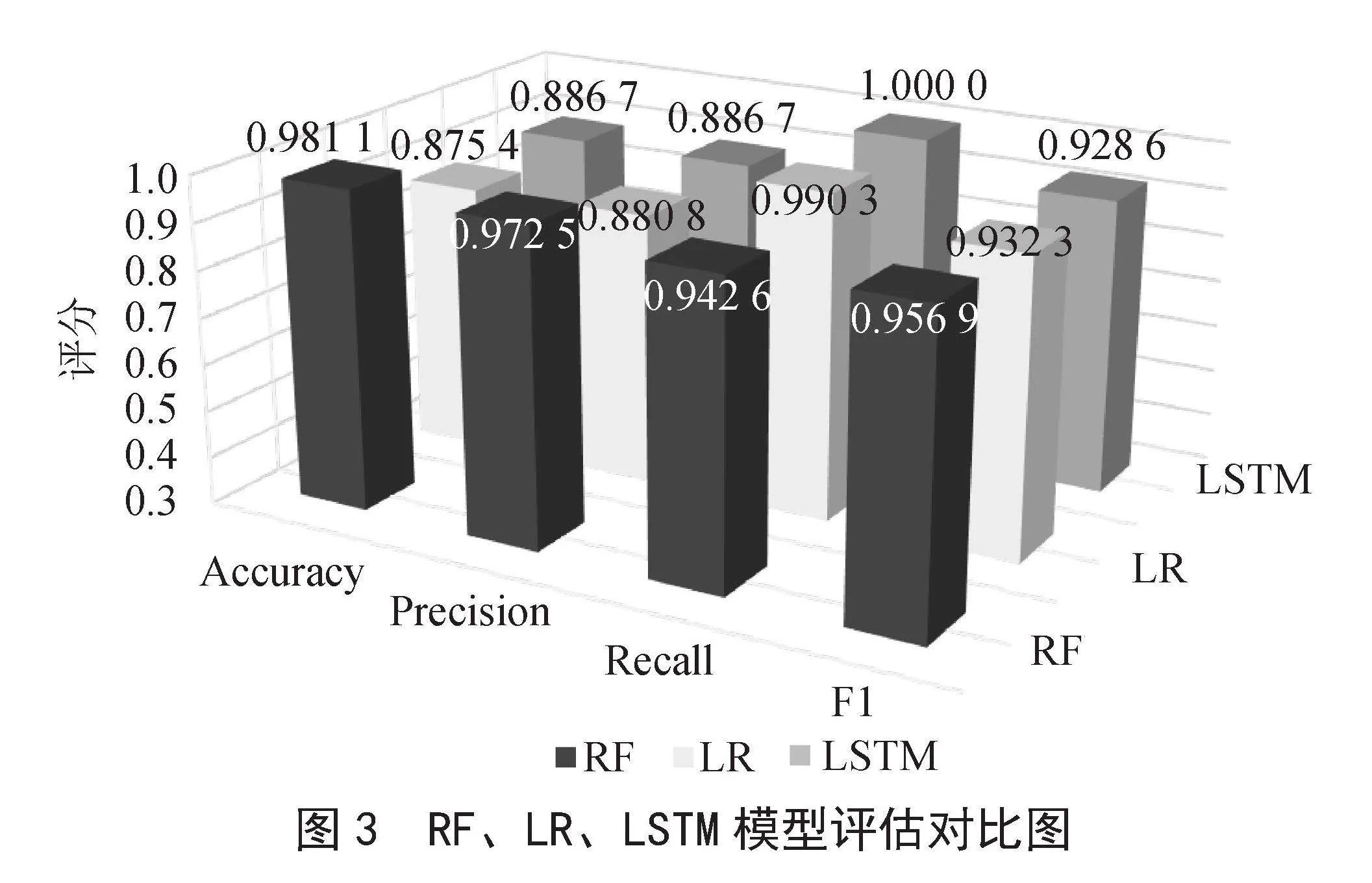

ModelSim软件仿真的FPGA工作频率及UART参数设置如表1所示。

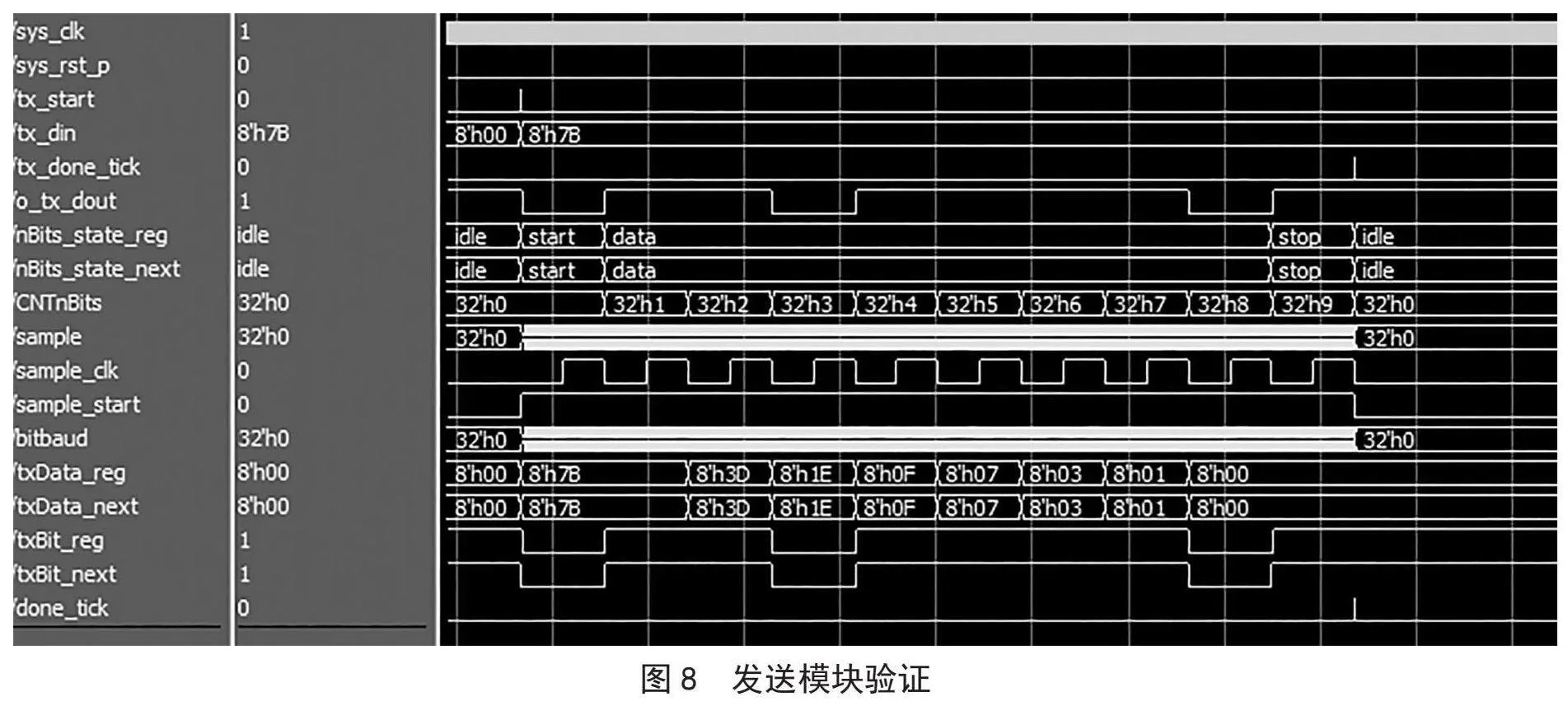

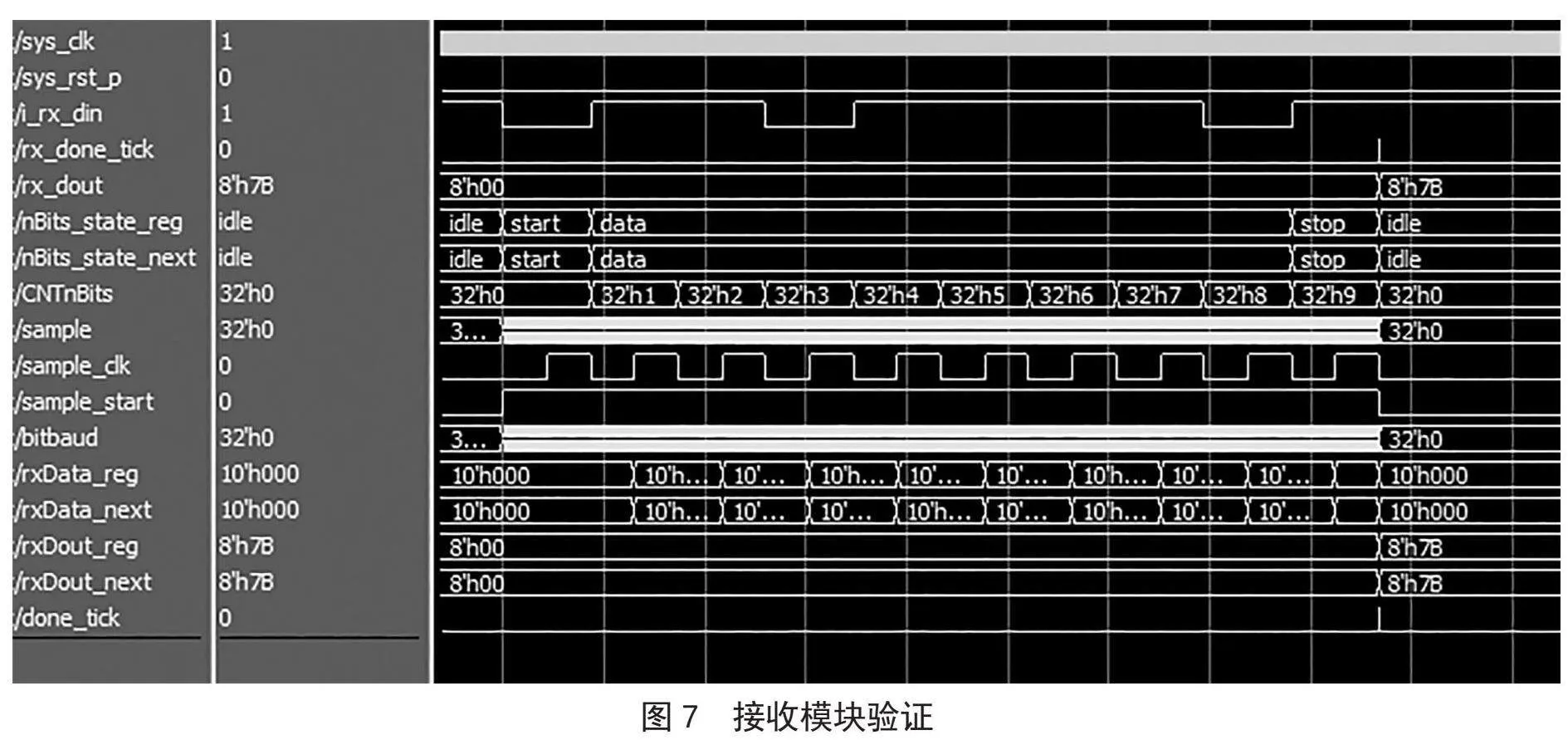

i_rx_din为数据输入端,将Testbench模拟数据(8h7B)的高低电平作为接收模块的输入端的输入信号,rx_dout为数据接收端,如图7所示。rx_dout接收数据的二进制表示形式为0111 1011。与i_rx_din输入端的数据8h7B高低电平一致,UART系统接收功能验证正确。

在接收模块完成数据接收后,将接收模块的完成标志doen_tick信号作为发送模块的tx_start信号。通过tx_start信号控制发送数据的开始,将tx_din的输入数据通过o_tx_dout端发送出。仿真结果显示:发射端o_tx_dout发送的高低电平与接收模块中i_rx_din输入的高低电平端相同,UART发送模块得到正确验证,整个系统的功能也得到验证,如图8所示。

4.2" 系统验证及验证结果

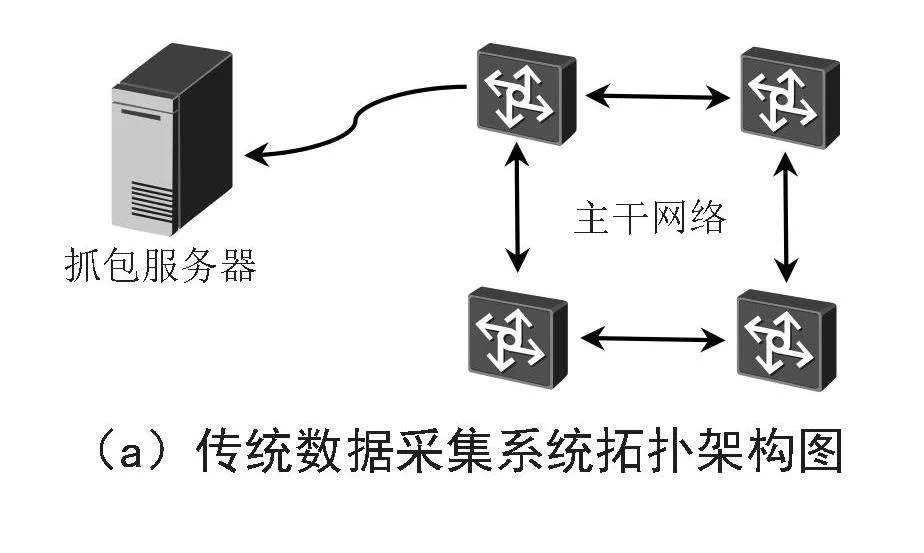

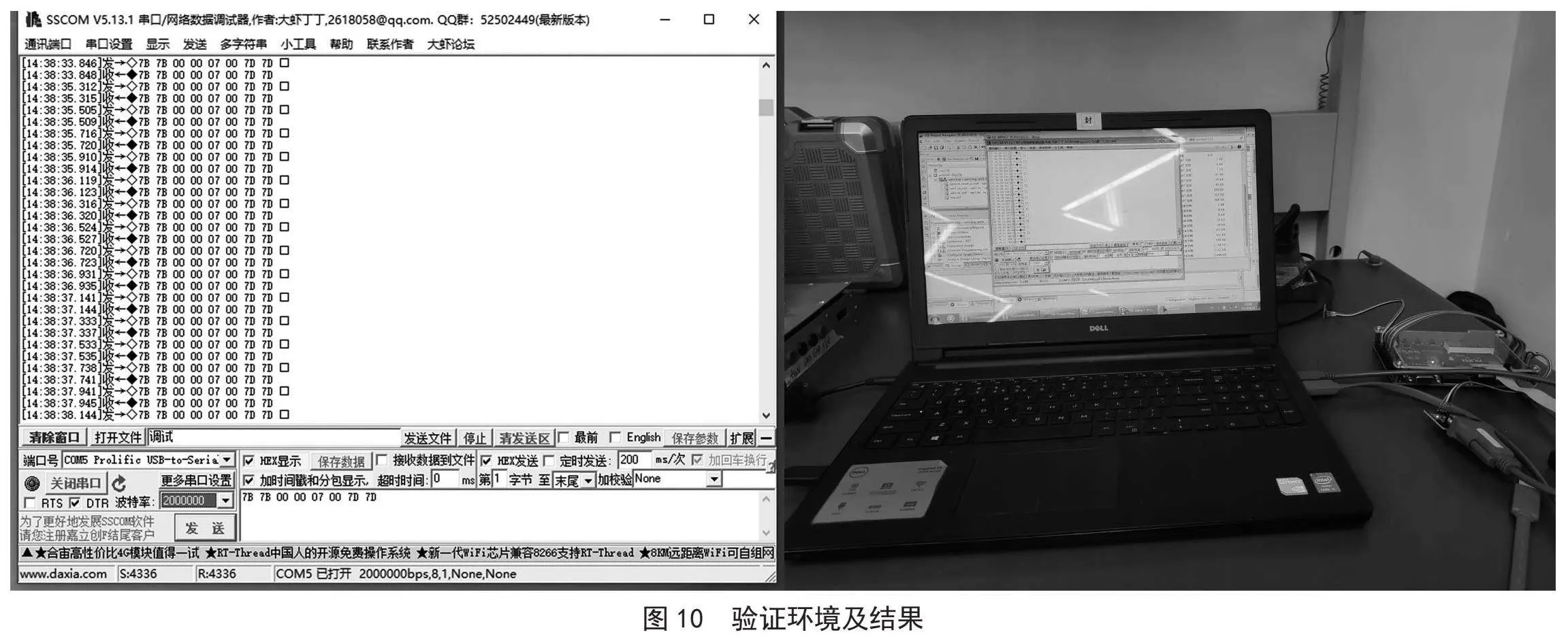

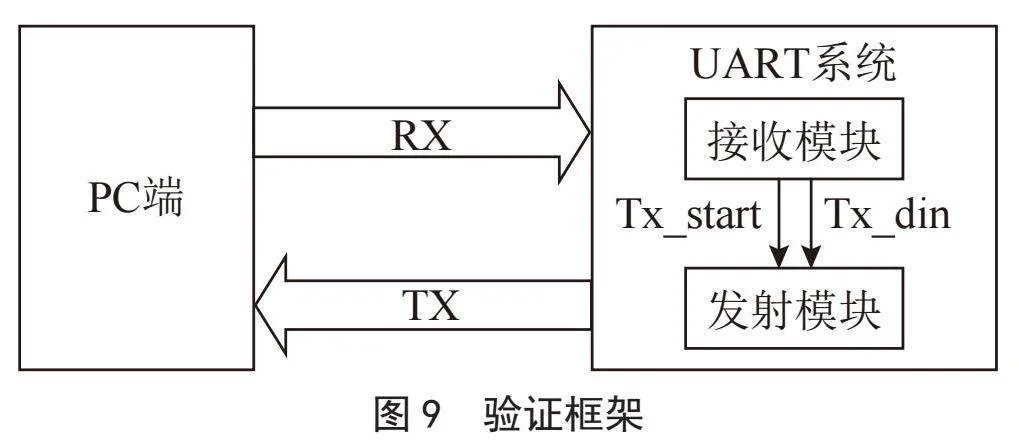

为进一步验证该系统设计的可行性,本文选用ALINX的AX309开发板,其FPGA选用Xilinx公司的XC6SLX9-FTG256BIV2037,其开发工具为ISE14.7。将开发板的TX端与RT端进行短接,通过串口调试助手工具进行数据的收发验证,其框架如图9所示。

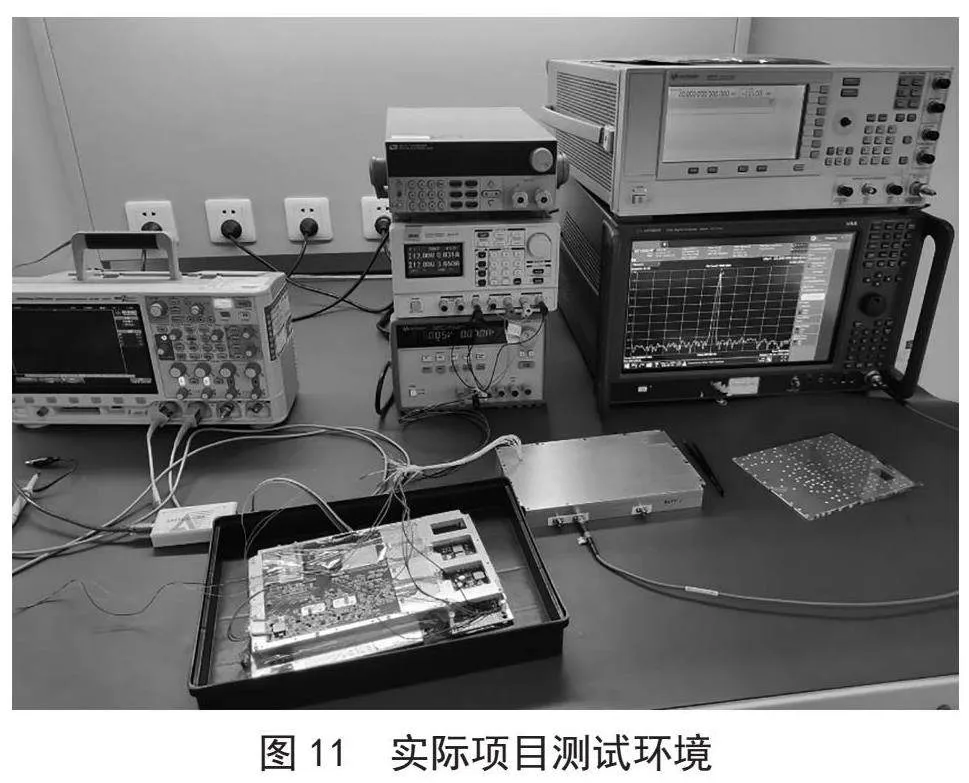

验证结果(如图10所示)表明,串口调试助手的发送数据与接收数据一致,UART系统的接收和发送功能正确。通过定时发送数据的接收结果,验证了UART功能的稳定性。并且,基于奈奎斯特采样的异步串行通信已应用于国产FPGA的实际项目中,经验证其工作稳定可靠,项目中使用的波特率为5 Mbit/s。实际项目测试环境如图11所示。

5" 结" 论

本文采用VHDL语言,在FPGA上设计和实现了基于奈奎斯特采样的异步串行通信接口,适用于1 200~5 000 000 bit/s波特率范围,对于高速UART通信,可以有效地进行数据接收和发送。与传统的实现UART通信的方法相比,基于奈奎斯特采样生成UART波特率的方法减少了无用检测及判决,降低了FPGA的逻辑资源消耗,还提高了系统的运行效率,增强了通信的可靠性和稳定性。在实际运用中,基于奈奎斯特采样的异步串行通信具有较强的可移植性,适用于Xilinx与国产安路的开发平台,具有很好的实际使用价值。

参考文献:

[1] 赵书安,周木春,葛超,等.基于国产芯片的雷达伺服多通信系统 [J].电子测量技术,2023,46(18):36-44.

[2] 胡立坤,王庆超.基于UART的可靠通信与性能分析 [J].计算机工程,2006(10):15-17+21.

[3] 吕阳,刘莉娜,郑良广,等.基于Verilog HDL的通用UART模块设计与实现 [J].电子设计工程,2020,28(8):174-179.

[4] 陈仁,王海英,华建文,等.基于FPGA的星载UART通讯设计与实现 [J].科学技术与工程,2015,15(13):212-217.

[5] 胥飞燕,郑华荣,周宦银,等.基于FPGA的多串口控制器的设计与实现 [J].物联网技术,2017,7(10):31–32.

[6] 刘博.基于FPGA的UART模块设计与实现 [J].无线电工程,2018,48(5):433-438.

[7] 丰淑凤,朱晓莹,王旭.基于FPGA的宽波特率误差容忍范围的UART设计 [J].信息技术与信息化,2021(9):169-171+176.

[8] 吴朝晖,曲立国.UART波特率检测电路的FPGA设计算法与实现 [J].现代电子技术,2022,45(20):41-44.

[9] 张名淑,张雅迪,王旭,等.基于FPGA的UART抗干扰接收装置设计与实现 [J].信息技术与信息化,2020(8):122-124.

[10] 王媛斌,王宏斌.FPGA与PC通信的UART串口设计 [J].兰州工业学院学报,2020,27(5):56-61.

[11] 杨澜,戚秀真.UART微控制器设计方法及其FPGA实现 [J].电子科技,2016,29(6):72-74.

[12] 王磊,李超,胡春喜.一种多功能通用异步串行UART接口的设计与实现 [J].四川兵工学报,2014,35(12):101-103+106.

[13] 李浩松,周寒冰,李明维,等.一种AD9371宽带无线同步定时模块简化方法 [J].电讯技术,2021,61(1):106-110.

作者简介:陈伟(1995—),男,汉族,四川广安人,硕士研究生在读,主要研究方向:信号检测与处理;通讯作者:蒲红平(1975—),男,汉族,四川广安人,副教授,博士,主要研究方向:大数据分析、智能控制、智能信号分析与处理、工业自动化研究与工程应用;杨仕勇(1989—),男,汉族,四川广安人,硕士研究生在读,主要研究方向:信号检测与处理和自适应控制;张淑慧(1998—),女,汉族,甘肃兰州人,硕士研究生在读,主要研究方向:信号检测与处理。