摘" 要:随着集成电路特征尺寸的不断缩减,存储电路中单粒子效应造成的多节点翻转的概率越来越大,严重影响了电路的可靠性。因此,为了增加存储电路的抗辐射加固能力和可靠性,提出一种三节点翻转加固锁存器TNUTL。该锁存器使用双模冗余和输入分离C单元实现100%三节点翻转容忍能力。钟控技术和传输门的使用有效降低了锁存器的功耗和延迟。32 nm CMOS工艺下的仿真结果表明,所提出的锁存器对比同类型结构平均降低了36.84%的功耗和65.31%的延迟,以及82.13%的功耗延迟积。

关键词:锁存器;C单元;软错误;三节点翻转

中图分类号:TN43;TP302.8" " 文献标识码:A" 文章编号:2096-4706(2024)09-0043-05

Triple-node Upset Tolerant Latch Design Based on Input-separated C-element in

32 nm Process

XIA Yu

(School of Computer Science and Engineering, Anhui University of Science and Technology, Huainan" 232001, China)

Abstract: As the feature size of integrated circuits continues to decrease, the probability of multi-node upset due to single particle effect in storage circuits is increasing, which seriously affects the reliability of the circuits. Therefore, to increase the radiation hardening capability and reliability of the circuit, a triple-node upset hardened latch, TNUTL, is proposed. The latch uses dual-mode redundancy and input separated C-element to achieve 100% triple-node upset tolerance. The use of clocking techniques and transmission gates effectively reduces the power consumption and delay of the latch. The simulation results under 32 nm CMOS process show that the proposed latch reduces power consumption by 36.84% and delay by 65.31% on average as well as power-delay product by 82.13% as compared to the same type of structure.

Keywords: latch; C-element; soft-error; triple-node upset

0" 引" 言

随着CMOS(Complementary Metal Oxide Semiconductor)工艺缩减至纳米尺寸,传统的锁存器越来越容易受到由辐射效应引起的软错误的影响[1]。当高能粒子轰击集成电路的敏感区域时,会产生大量的电子-空穴对,敏感节点会收集所产生的电荷,当收集的电荷量足够大就有可能导致节点的逻辑值发生改变,这一现象被称为单粒子翻转。集成电路特征尺寸的不断缩减会导致电路的集成度不断上升,晶体管之间的距离也不断缩小,因此单个高能粒子轰击电路所产生的电荷可能会被电路中的多个敏感节点收集,并导致其逻辑值发生翻转。这一现象又被称为单粒子多节点翻转。这其中又包括单粒子双节点翻转、单粒子三节点翻转等。资料显示[2],当集成电路进入90 nm之后,单粒子多位翻转的概率已经成为电路失效的主要原因之一。为此本文提出了一种32 nm CMOS工艺下三节点翻转加固锁存器设计。

针对大规模集成电路存储模块的加固,国内外进行了大量的研究,其中主要可以分为抗辐射加固设计[3]和抗辐射加固工艺[4]两种,其中抗辐射加固设计由于设计方法灵活且不需要构建专用工艺线因而应用最为广泛。本文所提出的锁存器设计即是基于抗辐射加固设计。在已有的锁存器加固设计中,C单元和DICE单元的应用最为广泛。以双输入C单元为例,当一个双输入C单元的两个输入相同时,它的输出刚好与它的输入相反。而当它的两个输入不同时,它的输出不会发生改变。因此如果它的两个输入中只有一个输入的逻辑值发生改变,则它的输出在一段时间内会保持原来的值不发生改变。我们可以认为在这种情况下错误会被C单元所阻塞。DICE单元由四个交叉耦合单元组成,由于内部的反馈回路使得DICE单元具备了单节点翻转自恢复的能力。

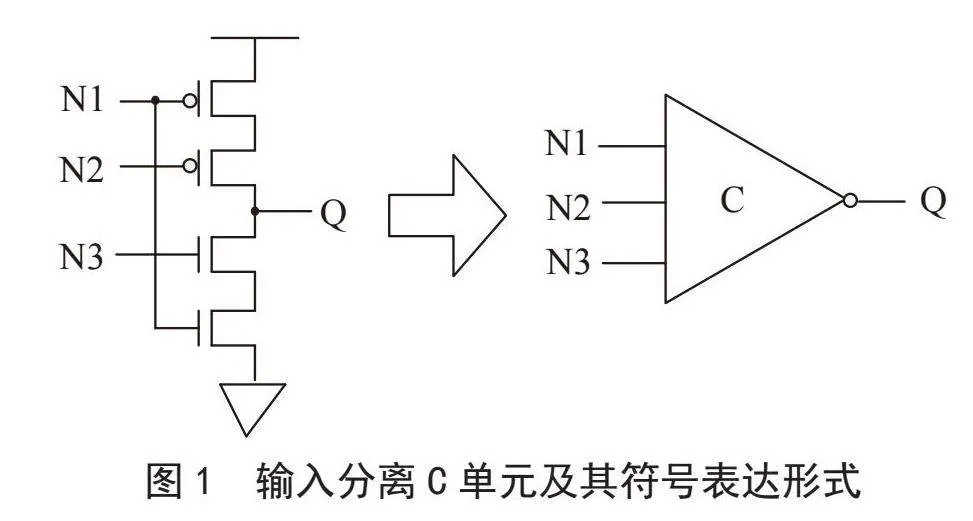

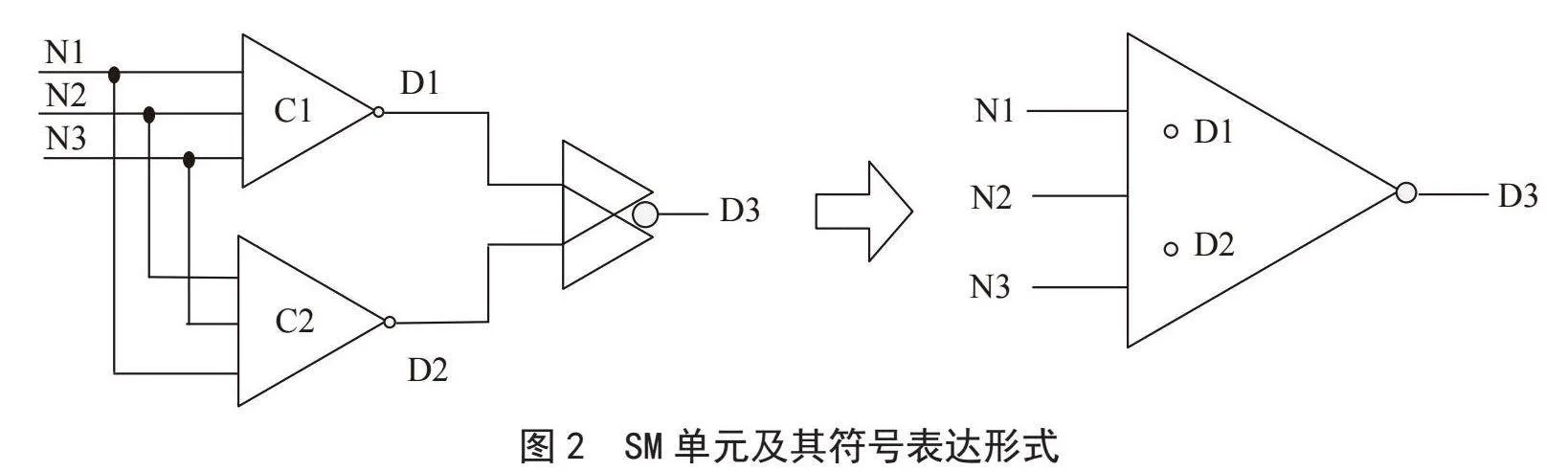

1" 输入分离C单元

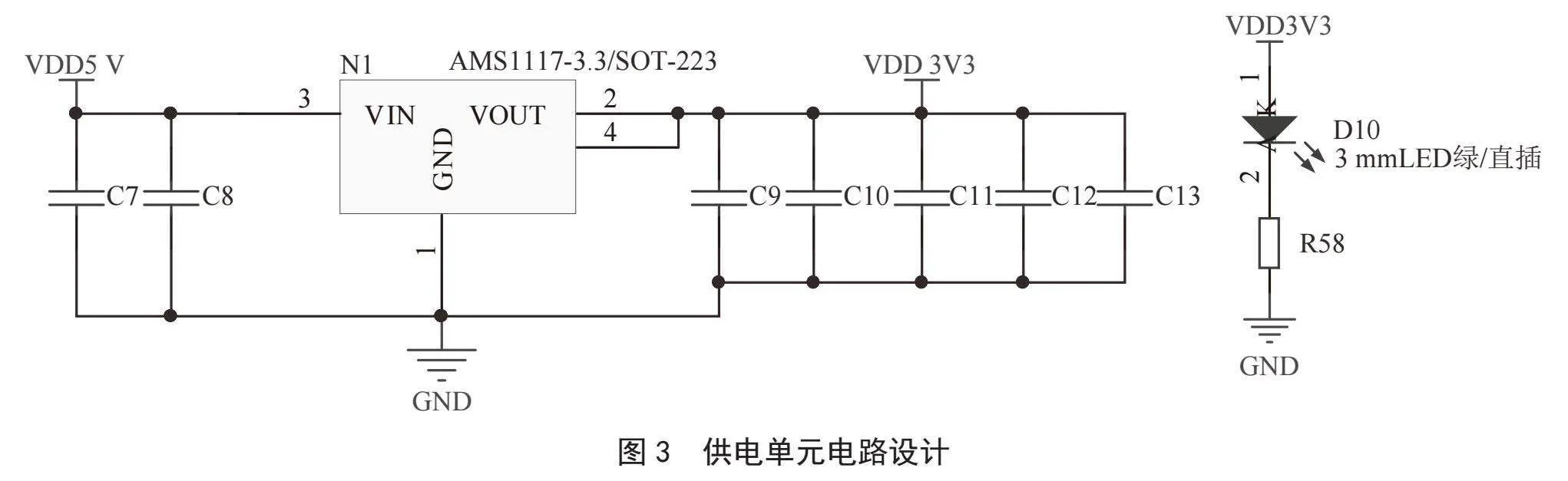

在原有C单元的基础上,通过增加一个输入即可得到输入分离C单元。在所提出的抗辐射加固锁存器设计中广泛使用了这一结构,它的电路结构如图1所示,从图中可以看出它将原来的双输入C单元的两个输入改为了三个输入,和双输入C单元的原理一样,输入分离C单元也可以阻塞输入端的错误。但是它有8种翻转情况。由两个输入分离C单元和一个双输入C单元就可以构成一个SM单元,其结构如图2所示。当它的三个输入节点N1、N2、N3任意一个节点发生翻转错误都不会传递下去,即输出端Q仍保持原来的逻辑值。当它的三个输入中有两个输入发生翻转时,最坏的情况下也只会导致D1或D2发生翻转。其余情况则不会影响到D1、D2、D3节点,即:

1)如果电路存储逻辑0时,N1、N2发生翻转会导致D2也发生翻转;如果N1、N3发生翻转,会导致D1发生翻转;其余六种情况下发生翻转的节点不会导致其余的节点发生翻转,即错误会被阻塞。

2)如果电路存储逻辑1时,N1、N2发生翻转会导致D1也发生翻转;如果N2、N3发生翻转会导致D2发生翻转;其余六种情况下发生翻转的节点不会导致其余的节点发生翻转,即错误会被阻塞。

2" TNUTL锁存器

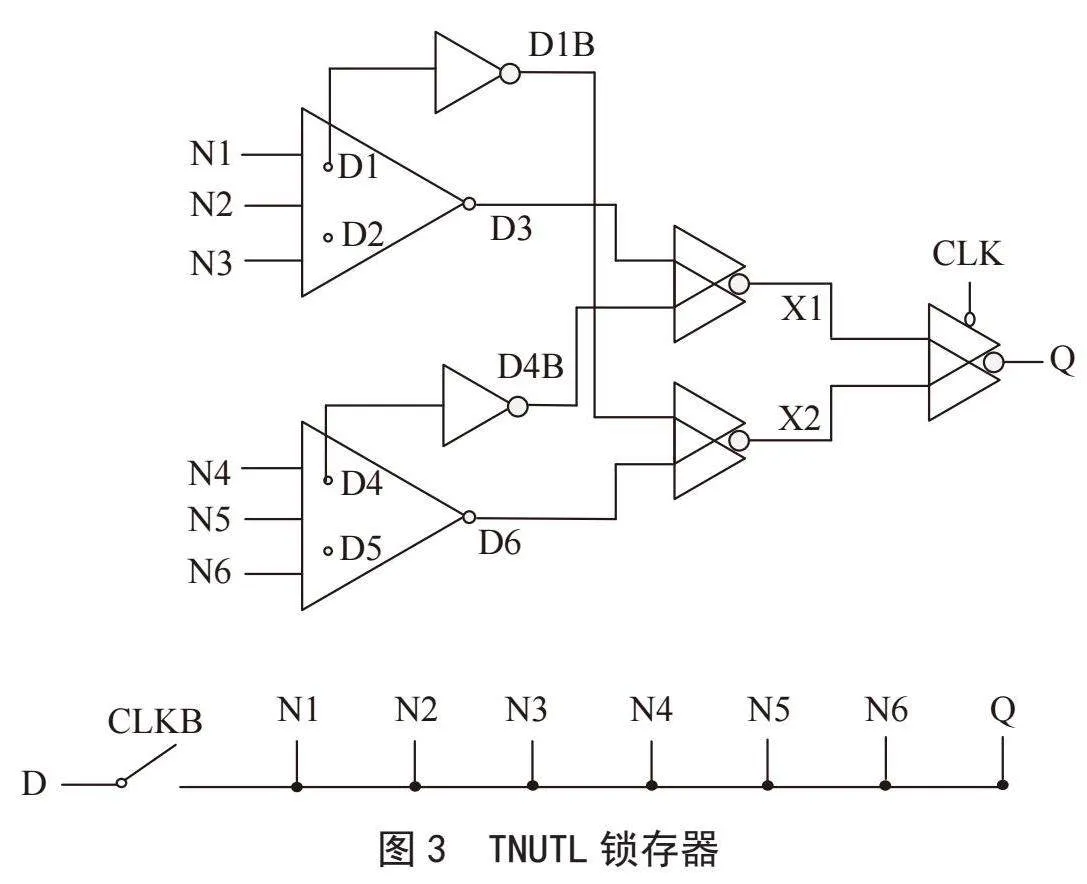

为了解决目前所存在的三节点翻转容忍锁存器功耗较大的情况,本文提出了一种新型的低功耗三节点翻转容忍锁存器,锁存器的结构如图3所示。锁存器使用由两个输入分离C单元和一个C单元组成的存储模块SM1、SM2和双层错误拦截模块组成,D和Q分别为锁存器的输入和输出节点,CLK和CLKB分别是系统时钟信号和负系统时钟信号。通过双层错误拦截模块可以将锁存期中锁存器内部发生的错误进行拦截,使输出Q节点保持稳定。

2.1" 锁存器的工作原理

锁存器的工作原理如下:当CLKB=0时,锁存器处于传输期,底部的传输门打开,输出级C单元关断,Q的状态由D通过底部的快速通路确定。当CLKB=1时,锁存器处于锁存期,此时底部的传输门会关断,而输出级C单元打开,Q由X1、X2确定,此时由于传输门关断,减少了由于电路竞争产生的功耗。

2.2" 锁存器的容错原理

由于锁存器并没有反馈回路的存在,因此当它的某一级输出节点发生翻转后并不会引起上一级输入节点的逻辑值的改变。同时由于C单元只有当它的所有输入节点发生翻转才会导致它的输出节点发生翻转的。因此当锁存器处于锁存期时除了N1~N6发生翻转不能恢复外,其余节点均可以恢复。

对于单粒子双节点翻转可以把它分为以下三种情况:

情况1:没有SM模块受到影响,此时只有一种情况即X1、X2、Q三个节点任意两个节点发生翻转,我们以<X1,Q>为例来说明,此时X1、Q均发生翻转,但SM1、SM2内部节点不受影响,因此X1会被恢复。接着Q会被恢复,因此本例中翻转的节点都将恢复。

情况2:一个SM受到影响,此时又可以分为以下两种情况:

1)一个SM模块内有两个节点受到影响。以<D1,D3>为例来说明,由于X1和X2不会受到影响,因此Q的值不会发生改变。而N1、N2、N3这三个节点不受影响,因此D1将会被恢复,相应的D1B也恢复。之后D3也将恢复,因此本例中翻转的节点将恢复。

2)一个SM模块内有一个节点受到影响,X1、X2、Q三个节点中有一个节点受到影响。以<D3,X1>为例来说明这种情况,由于X2此时不受影响,因此Q的值不会发生改变。同样,由于SM内部的其他节点没有发生改变,因此本例中翻转的节点会恢复。

3)两个SM受到影响。以<D3,D4>为例来说明。由于D4发生翻转,D4B也相应地发生翻转,之后X1将会发生翻转,但由于X2并未发生翻转,Q的值不会改变。同时由于SM模块内部其他节点并未发生改变,因此D3、D4将会恢复过来,D4B也将随着D4的恢复而恢复,因此本例中翻转的节点将会恢复过来。

单粒子三节点翻转这种情况可以分为以下三种情况:

情况1:没有SM模块受到影响,设<X1.X2,Q>受到影响。此时由于SM内部节点未受影响,因此本例中翻转的节点都恢复过来。

情况2:一个SM模块受到影响,此时可以分为以下三种情况:

1)一个SM模块内有三个节点受到影响。以<D1,D2,D3>为例来说明,Q的值保持未受影响不变,同时由于SM模块内的节点没有受到影响,因此D1、D2会先恢复,接着D3也将恢复,因此本例中翻转的节点都将恢复。

2)一个SM模块内有两个节点发生翻转,外部三个节点有一个节点发生翻转。以<D1,D3,Q>为例,此时<D1,D3>的情况在前面已经分析过了,而由于X1、X2节点未受影响,翻转的节点Q也将很快恢复,因此本例中翻转的节点都将恢复。

3)一个SM模块内部有一个节点受到影响,外部三个节点有两个节点受到影响。我们以<D3,X1,Q>为例,由于SM模块内部其他节点未受影响,因此D3将会恢复,相应的X1也将恢复。最终Q也会恢复。因此本例中翻转的节点都将恢复。

情况3:两个SM模块受到影响,这种情况可以分为以下两种情况:

1)一个SM模块内有一个节点受到影响,另一个SM模块内有两个节点受到影响。以<D1,D3,D6>为例来说明,首先发生翻转的三个节点会导致X2节点发生翻转,但此时Q不会受到影响,而<D1,D3>在前面已经分析过,在此不做赘述,D6节点和上面的SNU情况一样,因此本例中翻转的节点都将恢复过来。

2)两个SM模块各有一个节点受到影响,同时外部节点也有一个节点受到影响,以<D3,D6,Q>

为例,这种情况相当于两个SM模块发生SNU,因此发生翻转的两个节点都会恢复过来,同时由于X1、X2节点未受影响,Q也会恢复过来,因此本例中翻转的节点都将恢复过来。

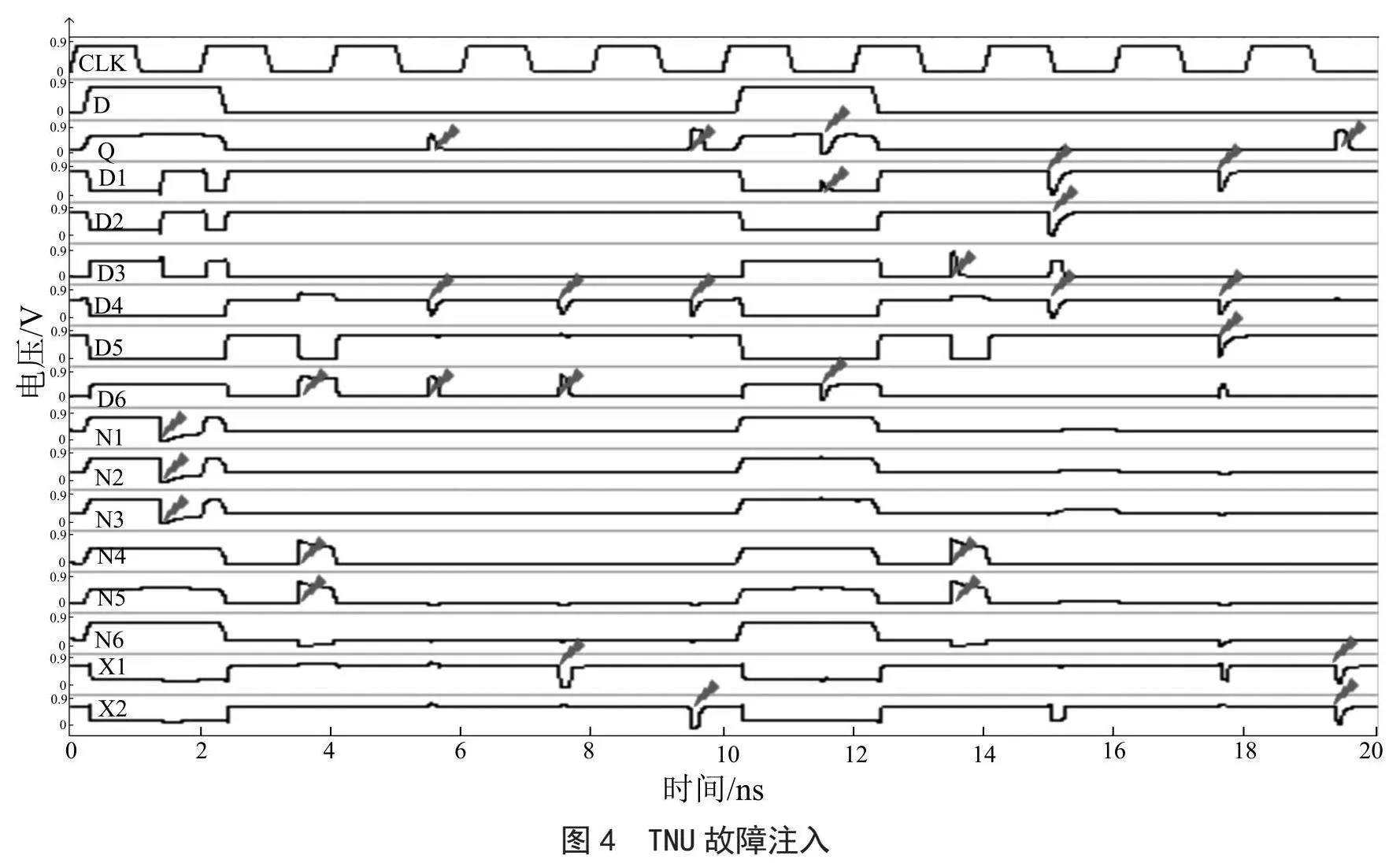

2.3" 锁存器的容错验证

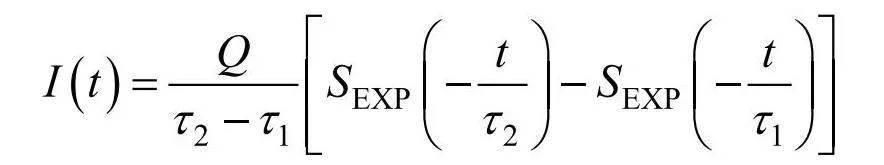

为了验证锁存器的容忍SEU(Single Event Upset)能力,在32 nm CMOS工艺模型下,使用HSPICE工具进行仿真,电源电压设置为0.9 V,温度设置为25 ℃,时钟频率为500 MHz。仿真中使用双指数电流源模型模拟粒子轰击所产生的瞬态脉冲,其中双指数电流源的算式如下:

其中:I (t)表示节点在某一时刻(t)所收集到的电荷而引发的电流,Q表示受到粒子轰击而收集到的临界电荷量,τ1和τ2分别表示离子轨迹建立时间常数和电荷聚集时间常数。波形图中红色闪电表示该时刻模拟遭受粒子轰击。

图4显示了锁存器注入TNU故障的情况,从图中可以看出,N1~N6的任一节点发生翻转都不会恢复过来,然而输出节点Q依然可以保持正确的逻辑值或者短暂发生翻转后又迅速恢复到正确的逻辑值。因此所提出的锁存器可以容忍任何情况的TNU。

3" 评估与对比

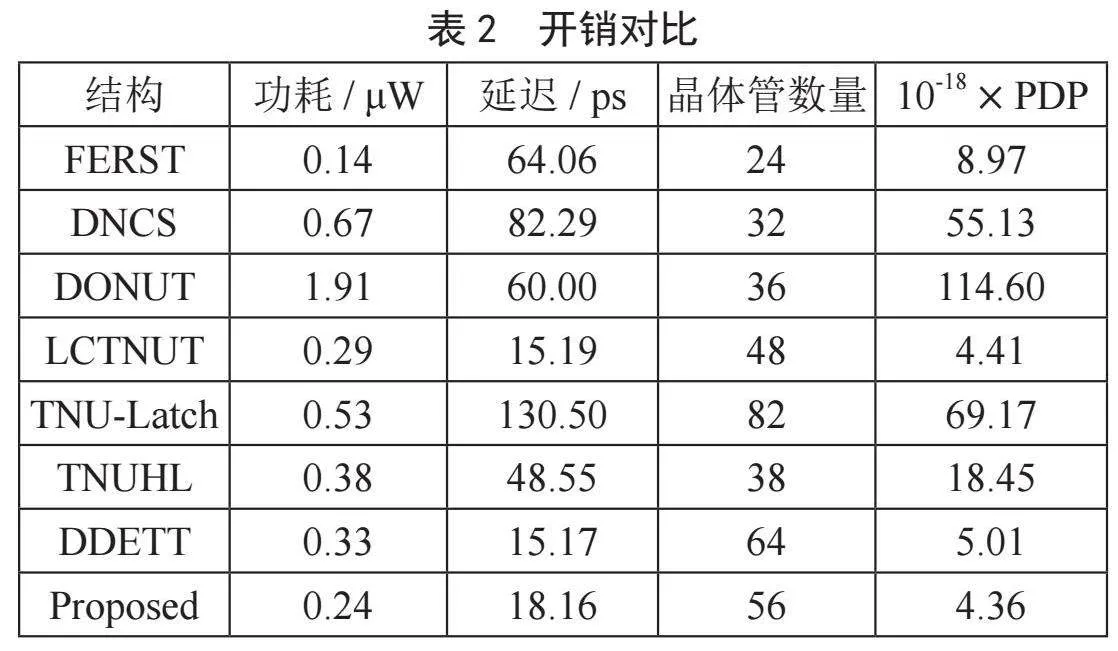

将所提出的锁存器与其他7种锁存器(FERST [5]、DNCS [6]、DONUT [7]、LCTNUT [8]、TNU-Latch [9]、TNUHL [10]、DDETT [11])进行了详细的对比分析。首先比较了上述锁存器的容错能力,包括SNU、DNU和TNU容错能力,接着对其性能与开销进行了对比,为了保证对比的公平性,所有锁存器都是在基于32 nm CMOS工艺下采用相同的电源电压和温度进行仿真。几种锁存器的加固能力对比如表1所示,从表中可以看出,本文所提出的锁存器与LCTNUT、DDETT、TNUHL、TNU-Latch属于同类型的锁存器,均可以容忍TNU,也就是说它们的加固能力最好。

这些锁存器的开销对比如表2所示,其中功耗是指在相同的输入下20 ns时间内整个电路结构所产生的平均功耗,延迟是指锁存期时输入D到达输出Q的数据传输延迟,PDP(Power-Delay -Product)指的是功耗面积乘积。从表中可以看出,所提出的锁存器在同类型的几种锁存器里具有最小的功耗和相对较小的延迟和晶体管数量。其中功耗延迟积越小代表电路的性能越好。从表中可以看出本文所提出的结构以牺牲部分面积开销为代价换取了功耗延迟的综合性最优。

为了更加直观地对比这些结构的开销对比,表3列出了所提出的锁存器和其他同类型锁存器的相对开销对比,其中∆ = 100%×(所提出结构-对比结构) /对比结构,如果最终的结果为正值,则表示所提出的锁存器的该项指标劣于对比结构,如果最终结果为负值则表示该项指标优于所对比的结构。从表中可以看到,相比四种同类型结构,文章所提出的结构平均降低了36.84%的功耗和65.31%的延迟以及82.13%的功耗延迟积。

4" 结" 论

本文提出了一种新型三节点翻转容忍锁存器TNUTL,通过双层错误拦截模块将锁存器内部的错误阻塞,使得输出端可以保持正确的逻辑值。在32 nm工艺模型下验证了本文可以容忍任意节点的SEU。与同类型的锁存器相比,本文所提出的锁存器以牺牲一定的面积为代价,有效降低了功耗与PDP。

参考文献:

[1] BAUMANN R. Soft Errors in Advanced Computer Systems [J].IEEE Design amp; Test of Computers,2005,22(3):258-266.

[2] DIXIT A,WOOD A. The Impact of New Technology on Soft Error Rates [C]//2011 International Reliability Physics Symposium.Monterey:IEEE,2011:5B.4.1-5B.4.7.

[3] 黄正峰,李先东,陈鹏,等.一种低开销的三点翻转自恢复锁存器设计 [J].电子与信息学报,2021,43(9):2508-2517.

[4] 王健安,谢家志,赖凡.微电子器件抗辐射加固技术发展研究 [J].微电子学,2014,44(2):225-228+236.

[5] FAZELI M,MIREMADI S G,EJLALI A,et al. Low Energy Single Event Upset/Single Event Transient-Tolerant Latch for Deep Submicron Technologies [J].IET Computers amp; Digital Techniques,2009,3(3):289-303.

[6] KATSAROU K,TSIATOUHAS Y. Double Node Charge Sharing SEU Tolerant Latch Design [C]//2014 IEEE 20th International On-Line Testing Symposium (IOLTS).Platja dAro:IEEE,2014:122-127.

[7] EFTAXIOPOULOS N,AXELOS N,PEKMESTZI K. DONUT: A Double Node Upset Tolerant Latch [C]//2015 IEEE Computer Society Annual Symposium on VLSI.Montpellier:IEEE,2015:509-514.

[8] YAN A B,LAI C P,ZHANG Y L,et al. Novel Low Cost, Double-and-Triple-Node-Upset-Tolerant Latch Designs for Nano-scale CMOS [J].IEEE Transactions on Emerging Topics in Computing,2021,9(1):520-533.

[9] WATKINS A,TRAGOUDAS S. Radiation Hardened Latch Designs for Double and Triple Node Upsets [J].IEEE Transactions on Emerging Topics in Computing,2020,8(3):616-626.

[10] KUMAR C I,ANAND B. A Highly Reliable and Energy-Efficient Triple-Node-Upset-Tolerant Latch Design [J].IEEE Transactions on Nuclear Science,2019,66(10):2196-2206.

[11] YAN A B,HE Z H,ZHOU J,et al. Dual-Modular-Redundancy and Dual-Level Error-Interception Based Triple-Node-Upset Tolerant Latch Designs for Safety-Critical Applications [J].Microelectronics Journal,2021,111(5):1-10.

作者简介:夏宇(1999—),男,汉族,安徽合肥人,硕士研究生在读,研究方向:锁存器的容错设计。