摘 要:针对多路高清视频信号实时处理中的画面叠加以及画中画显示实时性差的问题,设计了一种基于FPGA的多路视频实时处理系统。该系统可接收外部参数控制,并通过跨时钟域技术,实现了4路HDMI视频信号的输入接收、画面任意比例缩放、任意位置叠加以及画面漫游的实时处理功能。相比现有系统,该设计通过FPGA并行处理架构实现了多路高清视频的无缝实时叠加,提高了系统实时性能和显示效果,为多视频源的实时处理提供了一种新的系统解决方案。

关键词:多路视频;FPGA;跨时钟域

中图分类号:TP311 文献标识码:A 文章编号:2096-4706(2024)16-0024-04

Design of a Multi-channel Real-time Video Processing System Based on FPGA

Abstract: Aiming at the problems of poor real-time performance in overlay and picture-in-picture display of multi-channel high definition video signals, this paper designs a multi-channel real-time video processing system based on FPGA. The system can receive external parameter control. Through Clock Domain Crossing technology, the system implements real-time processing functions including input reception of 4 HDMI video signals, arbitrary aspect ratio scaling, arbitrary position overlay, and picture roaming. Compared with existing systems, this design achieves seamless real-time overlay of multi-channel HD videos through the FPGA parallel processing architecture, which improves system real-time performance and display effects. It provides a new system solution for real-time processing of multi-video sources.

Keywords: multi-channel video; FPGA; Clock Domain Crossing

0 引 言

随着工业自动化和智能化的不断发展,高清视频技术在工业监控领域的应用也日益增多。在工业监控中,实时高清视频处理不仅提高了监控效率,还增强了安全管理和质量控制的能力。特别是在涉及危险或难以接近的环境中,多路高清视频监控可以为操作人员提供实时、全面的视觉信息,帮助及时发现和处理潜在的安全隐患。然而,这些应用场景通常要求极高的视频处理实时性和稳定性,尤其是在需要对多个视频源进行同步分析和叠加时。因此,开发一种能够有效处理大量高清视频数据、同时保证低延时和高可靠性的系统,对于提升工业监控的效能至关重要[1-3]。

基于传统DSP和GPU架构的视频处理系统,受限于存储访问带宽和核心计算能力,难以满足多路高清视频实时画面叠加的处理需求。而基于FPGA的视频处理系统具有并行处理结构,可有效解决高清视频大量数据处理的问题[4-5]。

但是,在FPGA系统中实现多路视频的同步处理也面临时钟域划分以及存储访问冲突等问题。为实现多路高清视频信号无缝实时叠加,设计高效的跨时钟域技术以协调多路视频处理流程,优化DDR存储器访问机制以提供充足的存储读写带宽,是FPGA处理系统设计的关键[6-8]。

为此,本文设计了一种基于FPGA的多路高清视频实时处理系统。该系统在片上资源有效划分多个时钟域,实现低延时的多路视频画面无缝实时叠加。相比现有系统,本设计提供了一种高效可靠的多路高清视频实时处理方案,能够有效解决实时性和稳定性问题。

1 系统硬件设计

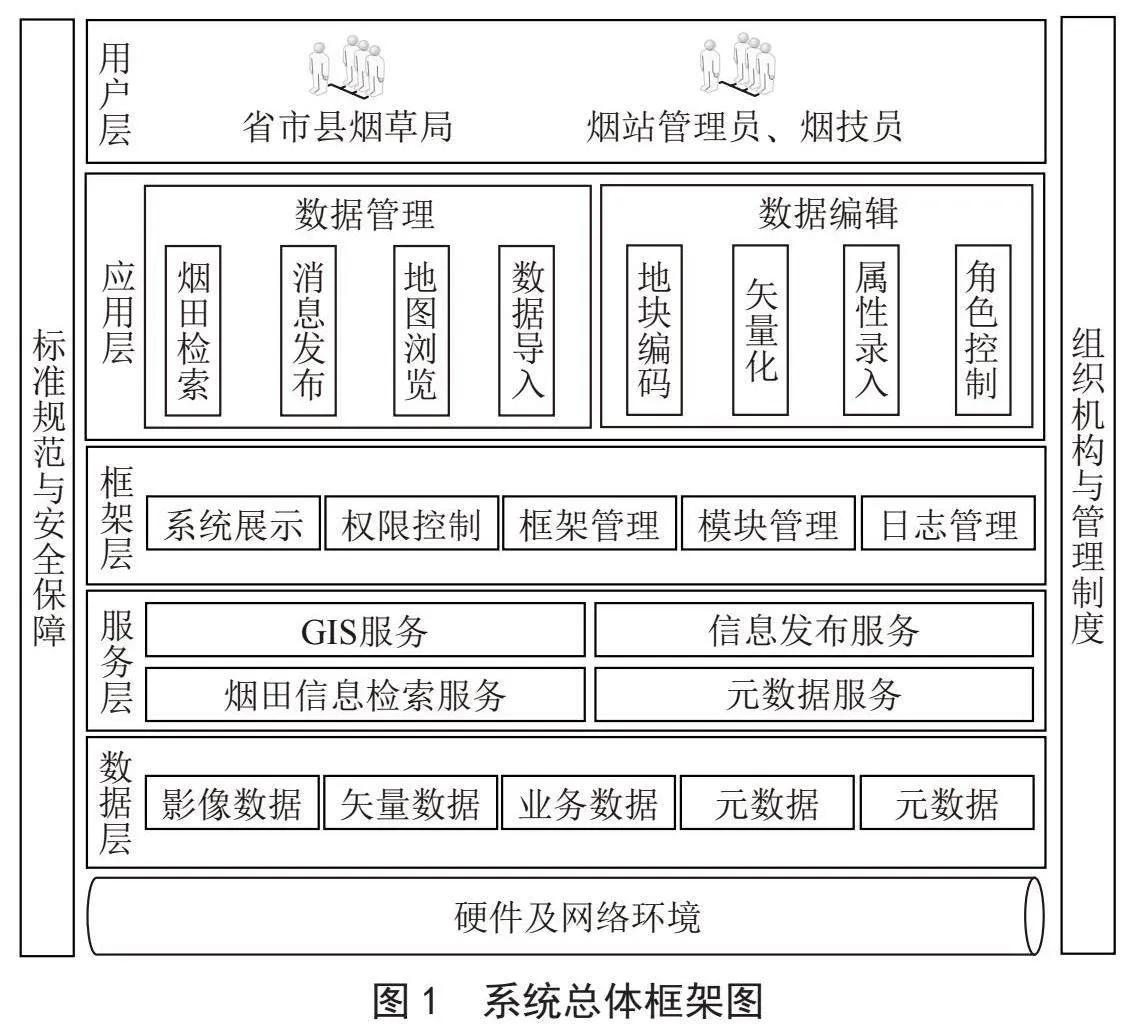

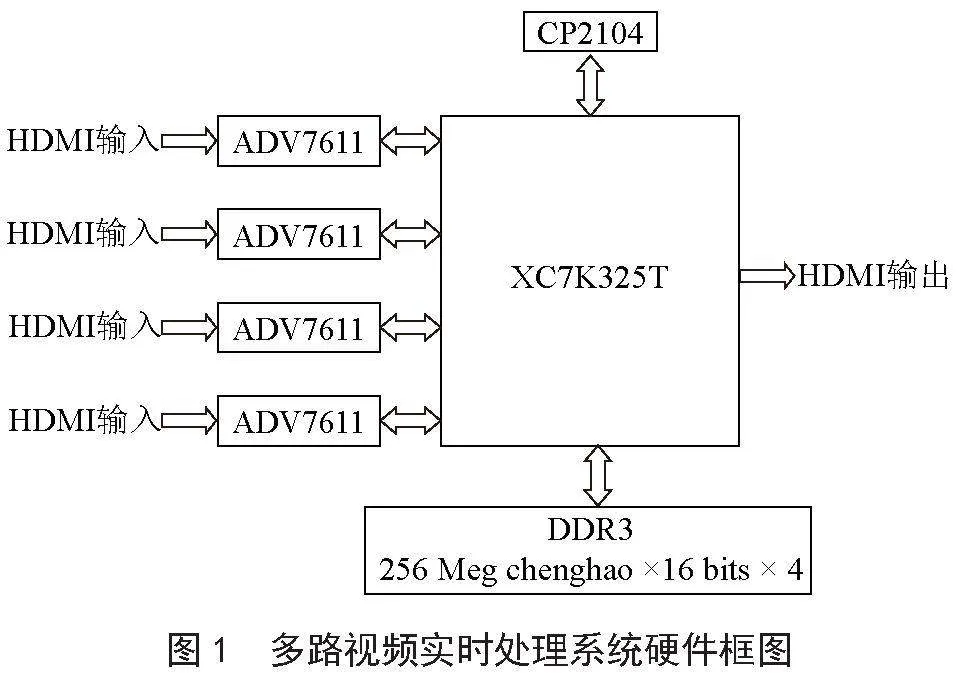

该系统硬件主要由Xilinx公司的Kintex-7系列FPGA XC7K325TFFG676、解码芯片ADV7611、串口芯片CP2104、DDR3存储芯片MT41K128M256等芯片组成。其系统硬件框图如图1所示。

在该系统中,FPGA首先通过I2C总线对视频解码芯片ADV7611进行配置初始化,完成寄存器参数的设置。配置完成后,系统输入的4路高清HDMI视频信号首先通过ADV7611解码芯片进行解码,输出RGB视频格式的数字信号。上位机通过USB串口(CP2104)将控制命令和参数传输到FPGA。FPGA根据接收到的控制指令,对输入的4路RGB数字视频信号进行裁剪、缩放等处理。处理后的视频数据通过帧缓存机制暂存到DDR3存储器中。最后,FPGA按时序读取DDR3存储器中的视频帧数据,转换成HDMI格式的视频信号输出。

2 多路视频实时处理系统程序设计

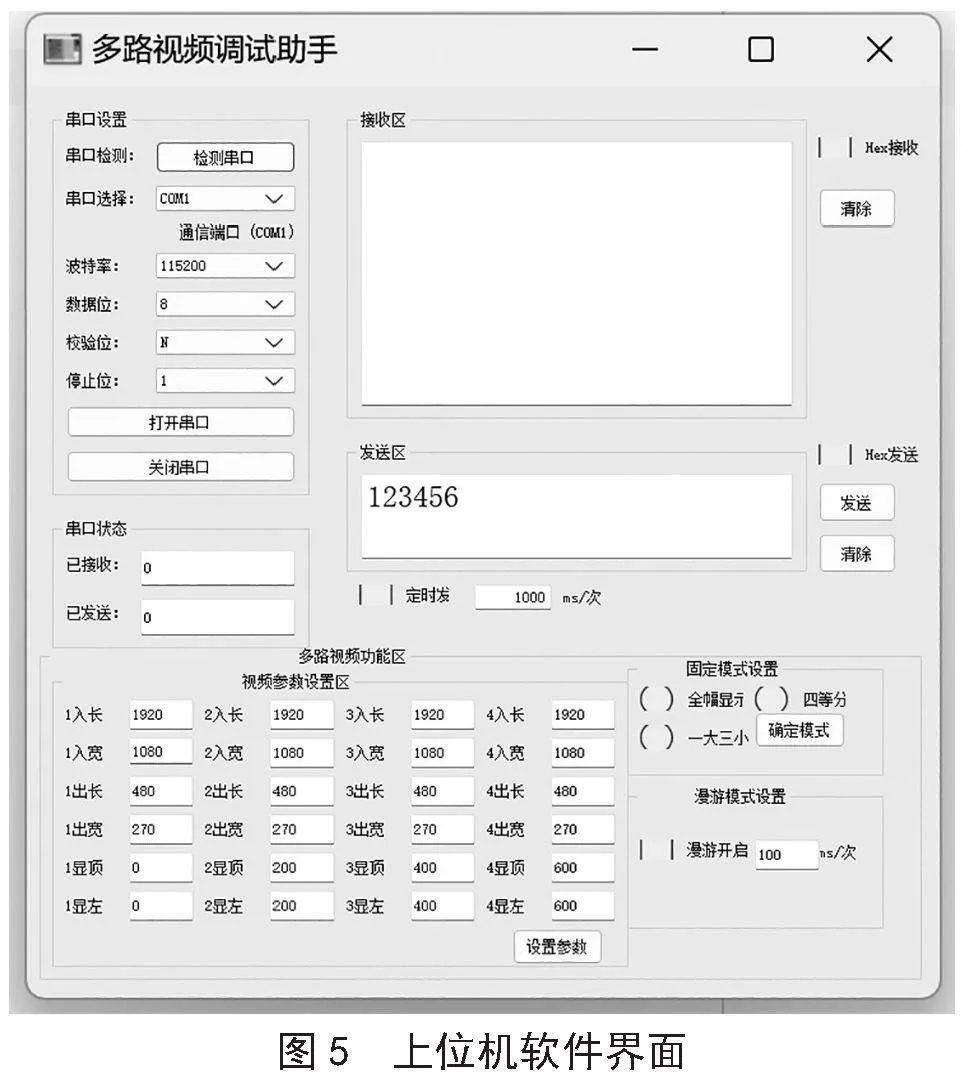

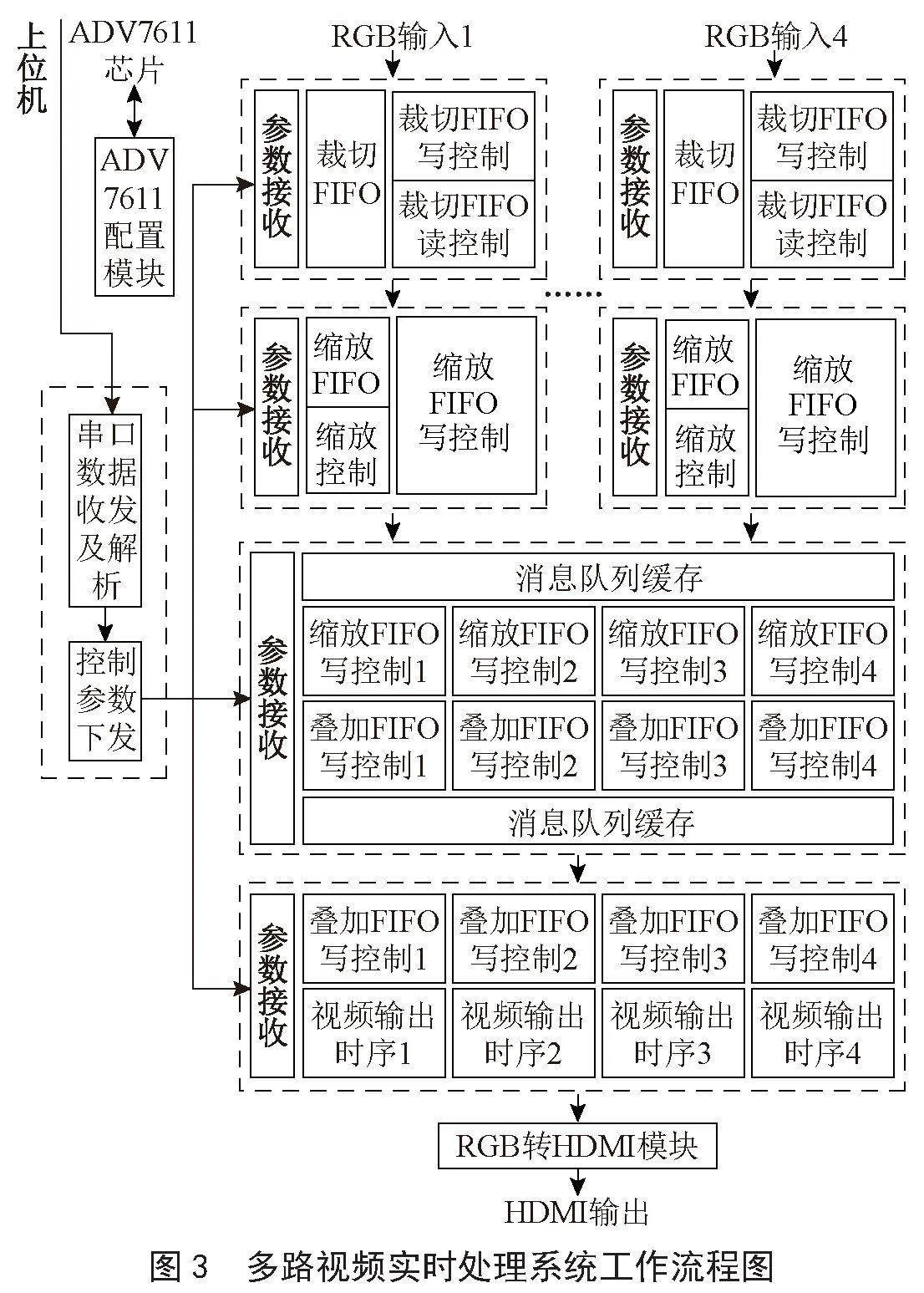

多路视频实时处理系统程序设计由FPGA完成,主要由系统参数初始化模块、ADV7611配置模块、视频裁剪模块,视频缩放模块、DDR3读写仲裁模块、视频叠加模块、RGB转HDMI模块组成。多路视频实时处理系统程序框图如图2所示。

系统上电时,ADV7611配置模块通过I2C总线对ADV7611进行配置,设置输出格式为GRB888,在参数设置完成后,产生一个ADV7611_Init_Done的信号,结合MIG IP核产生的init_calib_complete信号,共同作为系统复位信号。系统参数初始化模块随后将视频裁切默认参数、视频缩放默认参数、视频叠加默认参数下发。系统按照指定的剪切参数设置,通过视频输入像素时钟(pixle_clk)、视频输入使能信号(DE)、行同步信号(Hsync)、场同步信号(Vsync)将24位并行视频数据采集进异步FIFO中。之后,通过指定的缩放参数与双线性插值算法,完成视频数据的缩放。缩放后的数据通过异步FIFO,将24位位宽的RGB888数据首先通过补齐高8位来形成一个32位的数据,之后通过拼接处理将数据拼接为256位后,通过读写仲裁模块写入到DDR中。

在DDR读写仲裁模块中,需要分别进行4路视频数据写入操作和4路视频数据读取操作,这就对DDR仲裁读写操作提出了较高的要求。在本文设计的DDR读写仲裁模块中,首先使用message_queue消息队列模块来管理消息队列。消息队列模块首先通过双级触发器同步所有输入信号,以减少亚稳态的可能性并提高信号稳定性。接着,设计了一个三段式状态机来控制消息队列的状态转换,涵盖了空闲、各通道的读写以及等待状态,确保按照预定逻辑和顺序处理请求。为了在请求处理期间保持信号状态,模块使用寄存器缓存了每个通道的读写请求信号。当处理完某个通道的请求后,相应的缓存信号才会被清零。之后,DDR读写仲裁模块读取消息队列中的信息,确定当前的DDR操作模式、操作地址、突发读写长度,在完成单次DDR操作后,再次读取消息队列中的信息,进行下一次的DDR操作。该仲裁机制最大限度地减少了内存访问的延迟,提升了数据吞吐量,确保了在高负载条件下系统的稳定运行和高性能。

视频叠加模块接收到系统复位完成信号后,按照系统参数初始化模块指定的参数,首先生成一个对应分辨率的行同步信号、场同步信号及使能信号。之后,系统按照产生的视频同步信号,通过DDR读写仲裁模块将4路视频数据读出。数据读出后,首先将256位位宽的数据拆解8个32位位宽的RGB888的数据,之后按照指定的显示方式,通过级联的方式逐级产生视频时序与视频数据。最后,通过RGB转HDMI模块将RGB数据转为TMDS数据发送出去。多路视频实时处理系统工作流程图如图3所示。

3 跨时钟域信号同步设计

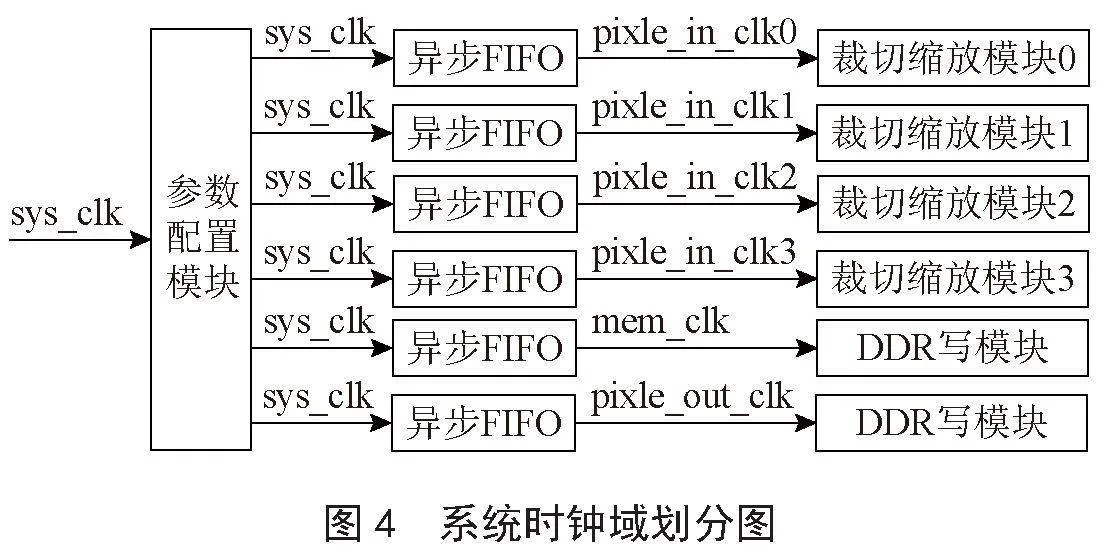

多路视频实时处理系统中存在多个时钟源:系统工作100 Hz系统时钟sys_clk、4路HDMI转RGB后的148.5 Hz像素时钟pixle_in_clk0、pixle_in_clk1、pixle_in_clk2、pixle_in_clk3、DDR3使用的200 MHz用户时钟mem_clk、视频叠加模块使用的148.5MHz输出像素时钟pixle_out_clk。在FPGA多路视频处理系统中,正确进行时钟域划分和管理对于整个系统的性能和稳定运行非常重要。由于不同模块或IP核心的工作时钟频率各不相同,在数据传输时就需要进行频域转换。如果直接进行不同时钟域间的相互访存、操作,将导致严重的时序问题,使系统产生时序故障。特别是对于数据量吞吐量大的视频处理系统,其数据传输和操作涉及多个不同频率的时钟域。跨时钟域的异步处理技术可以协调多个视频处理模块的工作时序,避免数据竞争和传输错误,保证视频数据能够在不同模块间精确流水线传输,从而大幅提高系统的数据吞吐量和稳定性[9-10]。

本系统中涉及跨时钟域的数据传输均为多比特数据传输,所以使用异步FIFO来完成。系统参数初始化模块与视频裁剪模块通过异步FIFO完成裁剪参数的传输;系统参数初始化模块与视频缩放模块完成缩放参数的传输;系统参数初始化模块与视频叠加模块完成开窗位置、开窗大小等参数的传输。系统时钟域划分图如图4所示。

4 上位机软件设计

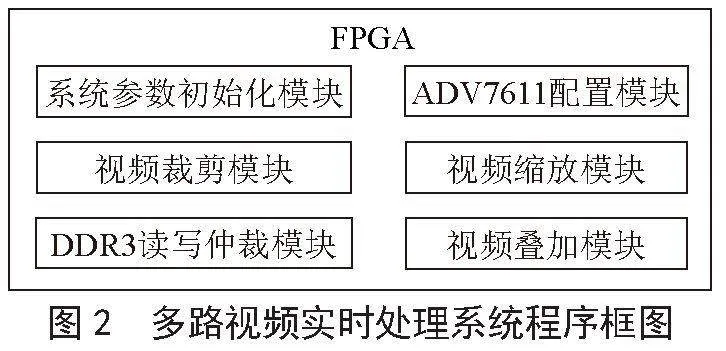

该系统的上位机软件采用Python+PyQt 5编程完成。PyQt 5是一套专为Python语言设计的图形用户界面(GUI)软件开发框架。PyQt5提供了超过600个类以及6 200个函数和方法,使得开发者能够轻松地构建具有丰富交互性的应用程序。PyQt5不仅支持Python 2和Python 3,并且作为一个跨平台的工具包,它可以在Windows、Mac OS、UNIX等多种操作系统上运行。

上位机软件能够实现显示模式的命令下发、回传信号的接收等功能。在该软件中,用户能够方便地实现固定显示模式的设置,例如单画面的全幅显示、4画面等分显示、1大三小显示等,同时还支持画面漫游显示功能。对于有特殊显示需求的场景,软件内设有视频参数设置区,用户可分别设置4路输入视频的输入分辨率、缩放后的显示大小、缩放后的显示位置信息,实现特殊的现实需求。上位机软件界面如图5所示。

5 系统搭建与验证

本系统支持4路全高清视频信号的输入和1路高清视频输出。在测试中,使用能输出1 920×

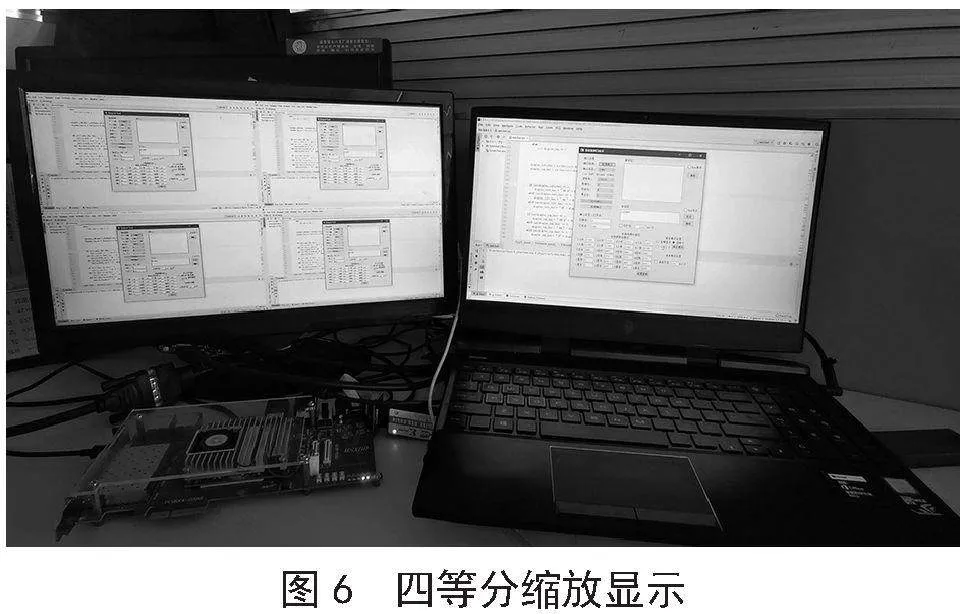

1 080@60Hz高清视频的笔记本作为视频源,通过FPGA内部逻辑实现将1路高清视频输入复制并扩展为4路高清视频信号。笔记本通过串口连接至信号板上,打开上位机软件,设置显示模式,FPGA即将处理后的视频信号通过HDMI接口输出到显示器上进行显示。如图6所示,系统能够实现4等分缩放显示。如图7所示,系统能够实现可调比例可调位置缩放显示。

6 结 论

本文设计并实现了一种基于FPGA的多路高清视频实时处理系统。该系统通过FPGA并行处理结构,有效解决了高清视频大数据量处理的难题,实现了多路HD视频信号的实时裁剪、缩放和叠加处理。系统采用ADV7611视频解码芯片接收HDMI视频源,经处理后通过DDR3存储器进行缓存,并最终转换为HDMI格式的输出。

关键的跨时钟域技术应用确保了系统各处理模块之间的精确数据传输与同步,避免了多频率异步时钟之间的时序故障。系统采用异步FIFO进行视频数据的跨时钟域传输,相比直接逻辑传输,这种方法大幅减少了时序约束压力,保证了稳定可靠的数据传输。

测试结果表明,该系统实现了实时处理4路高清1080P视频,并具备任意画面分割、缩放以及多画面叠加显示等功能,整个系统保证了低延时的多路高清视频无缝实时处理效果。

本设计的基于FPGA的多路高清视频实时处理系统,不仅在技术上实现了多路视频信号的高效实时处理,而且具有重要的工业应用价值。在工业监控领域,该系统可以显著提高监控效率和安全性,特别是在对实时性要求高的环境中,如自动化生产线、关键基础设施监控以及危险区域的安全监视。系统的低延时处理能力确保了紧急情况下可以迅速响应,为工业监控领域提供了一种高效、可靠的视频处理解决方案,展示了在高要求工业环境中实现精确和实时监控的巨大潜力。

参1g6MPy7HI5r8TuKTXsi08tQp15JUXFELamHInGYBiBo=考文献:

[1] 宋长骏,汤勇明.基于FPGA的通用多路视频输入处理系统设计 [J].电子器件,2022,45(4):805-809.

[2] 王轶楷.实时视频图像缩放系统的FPGA硬件实现 [D].太原:中北大学,2023.

[3] 严飞,丁兆东,刘银萍,等.基于FPGA的多路实时视频处理系统设计 [J].液晶与显示,2022,37(7):861-870.

[4] 刘洪庆.机载多路视频采集设备设计与实现 [J].中国电子科学研究院学报,2021,16(10):1029-1033.

[5] SUN K C,KOCH M,WANG Z,et al. An FPGA-Based Residual Recurrent Neural Network for Real-Time Video Super-Resolution [J].IEEE Transactions on Circuits and Systems for Video Technology,2021,32(4):1739-1750.

[6] 吝毅.基于FPGA的实时图像预处理系统研究 [D].西安:长安大学,2023.

[7] COSTA A,CORNA N,GARZETTI F,et al. High-Performance Computing of Real-Time and Multichannel Histograms: A Full FPGA Approach [J].IEEE Access,2022,10:47524-47540.

[8] 张丽红.基于FPGA的多路音视频控制系统的实现 [J].电子元器件与信息技术,2021,5(10):96-98.

[9] JAIN D K,JACOB S,ALZUBI J,et al. An Efficient and Adaptable Multimedia System for Converting PAL to VGA in Real-Time Video Processin [J].Journal of Real-Time Image Processing,2020,17:2113-2125.

[10] 昱人.车载多路视频记录与回放系统设计 [D].太原:中北大学,2020.