摘" 要:文章对串行通信收发器抗干扰芯片设计进行了研究。针对现有CAN/RS485收发器芯片在高干扰环境下通信不稳定的问题,提出一种基于自适应滤波技术的抗干扰芯片设计方案。该方案采用极简设计原则,通过对现有芯片架构的微小改动,在芯片内部引出分压网络的两端,并外接电容形成一阶RC低通滤波器,可有效抑制共模和差模干扰。仿真和实测结果表明,所设计的芯片能显著改善抗干扰性能,大幅提高串行总线通信的可靠性和稳定性。该方案完全兼容现有接口标准及使用习惯,在电力、工业自动化、新能源、汽车电子等领域具有广阔应用前景。

关键词:串行通信;抗干扰;自适应滤波;芯片设计;CAN/RS485

中图分类号:TN402" 文献标识码:A" 文章编号:2096-4706(2024)23-0001-05

Design of Anti-interference Chip of Serial Communication Transceiver with Adaptive Filtering Technology

ZHANG Shuhong

(Shenzhen Clou Electronics Co., Ltd., Shenzhen" 518057, China)

Abstract: The paper conducts research on the design of anti-interference chip of serial communication transceiver. Aiming at the problem of unstable communication in the high interference environment for the existing CAN/RS485 transceiver chip, it proposes an anti-interference chip design scheme based on adaptive filtering technology. The scheme adopts a minimalist design principle, by making minor modifications to the existing chip architecture, leads out the two ends of the voltage divider network inside the chip, and connects an external capacitor to form a first-order RC low-pass filter, which can effectively suppress common-mode and differential-mode interference. Simulation and test results show that the designed chip can significantly improve anti-interference performance and greatly enhance the reliability and stability of serial bus communication. The scheme is fully compatible with existing interface standards and usage habits, and has broad application prospects in fields such as electric power, industry automation, new energy, and automotive electronics.

Keywords: serial communication; anti-interference; adaptive filtering; chip design; CAN/RS485

0" 引" 言

RS485/CAN等串行总线因其多点接入、布线简单、容错能力强、成本低等特点,在电力、工业自动化、新能源、汽车电子等领域得到广泛应用。然而,在实际使用中,这些领域往往存在严重的电磁干扰问题,导致设备通信不稳定甚至瘫痪。本文提出一种自适应滤波技术的串行通信收发器抗干扰芯片设计方案,通过极小的电路改动,即可大幅改善抗干扰性能,为提高系统可靠性提供了一种简单有效的解决方案。

1" 串行总线电磁干扰问题分析

1.1" 开关电源、变频器等设备引入的干扰特征

开关电源和变频器等设备内部功率开关器件的高速开关会产生高di/dt和dv/dt,导致严重电磁干扰。干扰通过传导、辐射、共模耦合等方式影响串行总线通信质量。典型干扰表现为尖峰脉冲,上升沿可达10 ns量级,幅值几伏到几十伏,持续时间小于50 ns,频率成分含高频分量,容易引起数据传输错误,导致通信不稳定或失败[1]。

1.2" 干扰对通信信号的影响及失效模式

电磁干扰通过共模和差模途径耦合至总线引起通信异常。共模干扰来自开关动作,通过地线、电源线、寄生电容耦合到信号线,表现为共模电压;差模干扰来自电源纹波、传输线不平衡及横向耦合,表现为信号线间电位差。干扰信号超过接收器容限范围时,引起接收错误,常见失效模式包括误码、丢包、重发、节点掉线等,干扰脉冲宽度小于位宽时,降低通信速率难以规避。

1.3" 常规抗干扰措施及其局限性

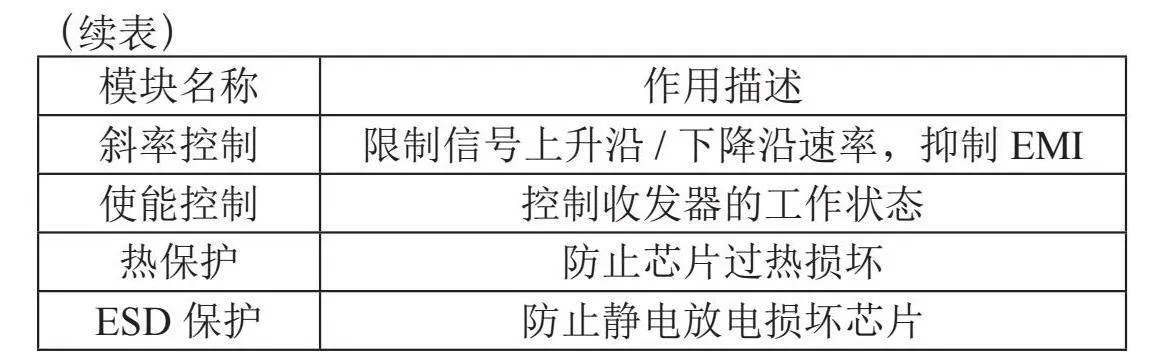

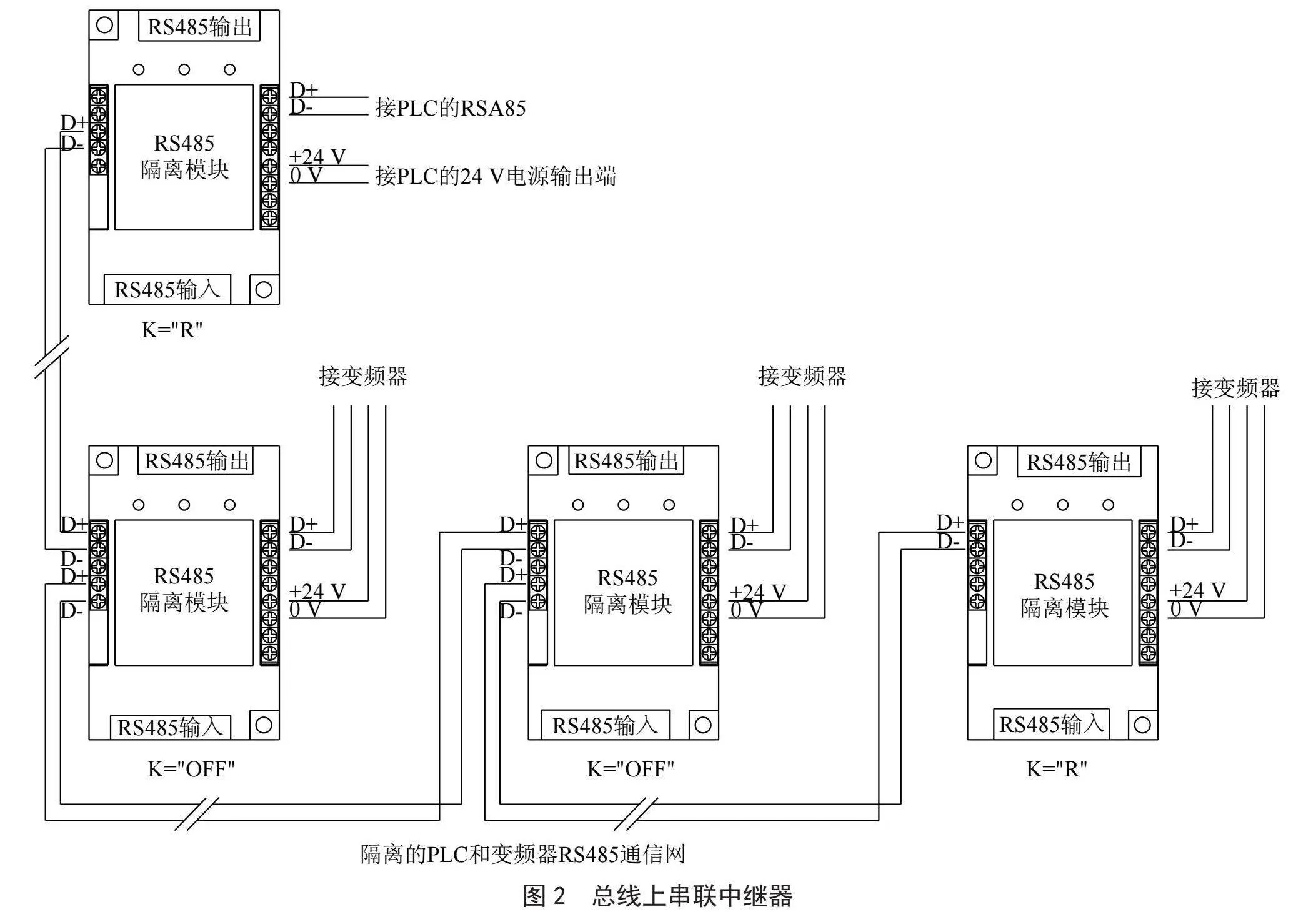

如图1、图2所示,传统抑制串行总线电磁干扰措施包括串联共模电感或磁环、加装隔离中继器、采用屏蔽双绞线、对开关电源加装EMI滤波器、优化PCB布局、对关键器件单独供电等。但这些措施各有利弊,如引入信号失真、成本高、布线复杂、抑制高频脉冲困难等,缺乏通用性和彻底性。随着电力电子技术发展,开关速度加快,电磁兼容问题日益突出,需要研究开发新型抗干扰接口芯片[2]。

2" 自适应滤波技术抗干扰芯片设计

2.1" 现有串行收发器芯片架构

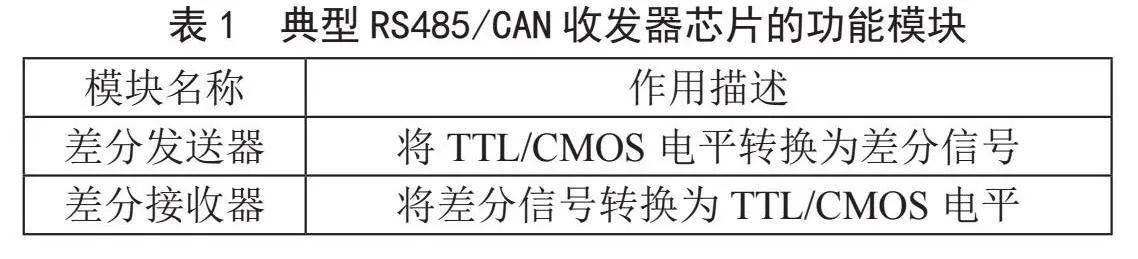

现有的RS485/CAN收发器芯片通常由差分发送器、差分接收器、斜率控制电路等模块组成。差分发送器负责将控制器输出的TTL/CMOS电平转换为总线所需的差分电平信号,一般采用H桥结构实现。差分接收器则将总线上的差分信号转换为控制器可识别的逻辑电平,主要由电阻分压网络和比较器构成。斜率控制电路用于限制信号上升沿/下降沿速率,以抑制电磁辐射。此外芯片还包括使能控制、热保护、ESD保护等辅助电路[3]。典型的RS485/CAN收发器芯片的功能模块如表1所示。

在接收端,差分信号首先通过一个电阻分压网络,由120 Ω电阻和两个10 kΩ电阻构成,在±12 V共模输入范围内,可将差分信号线性转换为0~5 V的CMOS电平,再经比较器判决输出。分压网络虽然具有削弱共模干扰的作用,但由于RC时间常数较小(约3 ns),对纳秒级脉冲干扰的抑制效果有限。同时10 kΩ高阻直接连接芯片内部,容易受到静电损伤。因此有必要对现有电路进行针对性的改进[4]。

2.2" 改进方案及其设计思路

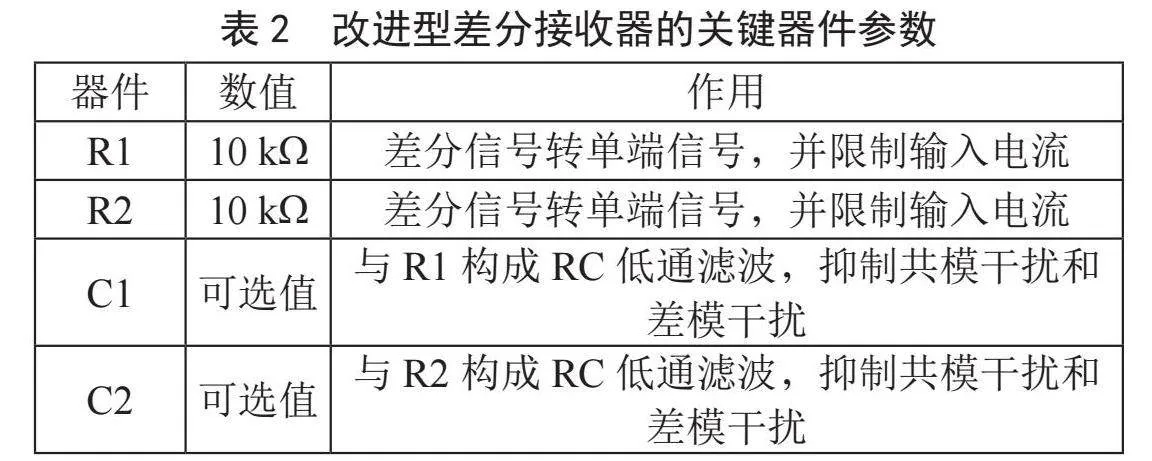

针对RS485/CAN总线面临的高速脉冲干扰问题,本文提出一种自适应滤波技术的抗干扰芯片设计方案。其核心思路是在差分接收器电路的电阻分压网络后级联一个可调的RC低通滤波器,并将滤波器的输入和输出端口引出芯片,通过外接电容的方式实现滤波时间常数的可调。改进后的差分接收器电路如表2所示,其中R1/R2为分压电阻,C1/C2为外接滤波电容。

该电路利用R1/C1和R2/C2构成的RC低通滤波器,其截止频率fc满足:

fc = 1/(2πR1C1)=1/(2πR2C2),通过选择合适的外部电容值,可将截止频率设置到1 MHz以下,从而有效抑制纳秒级干扰脉冲,且不影响10 Mbit/s以下的通信速率。同时将分压电阻的中间节点引出芯片,可避免高阻直接连接内部电路,降低静电损伤风险。

值得一提的是,外接电容的引入并不增加额外的引脚数量。因为可利用原本用于限制EMI辐射的Cs引脚,在不需要时可悬空处理。该改进方案完全兼容现有的RS485/CAN物理层标准和接口规范[5]。

2.3" 关键电路的仿真分析

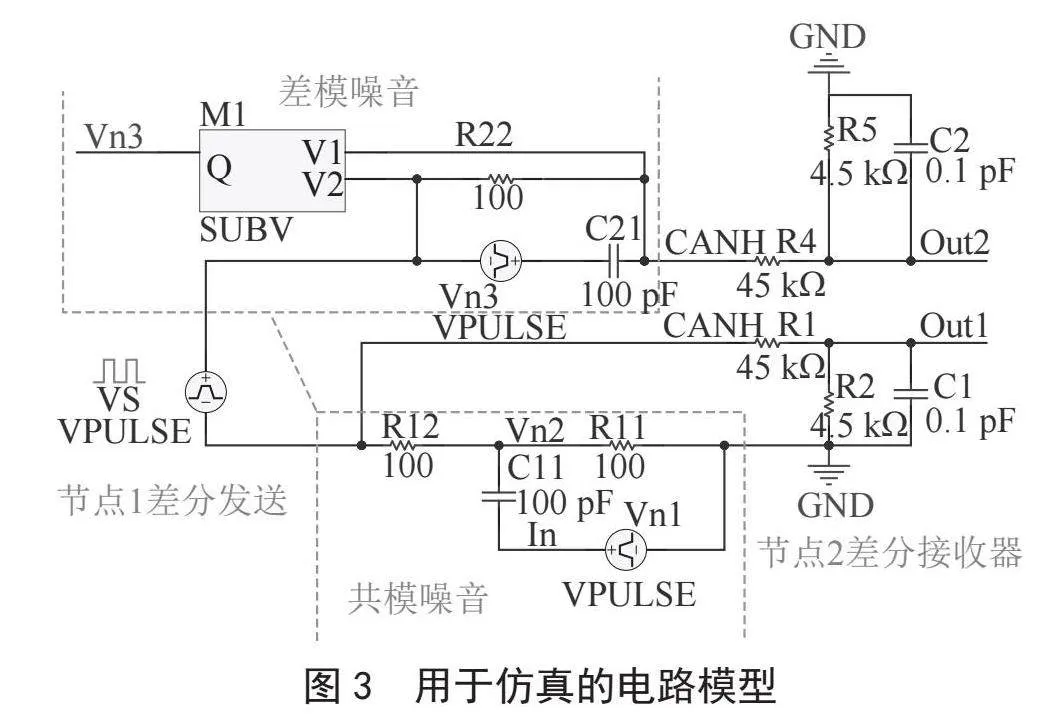

为验证所提出的抗干扰芯片设计方案的有效性,本文在Pspice中搭建了差分接收器的仿真电路,如图3所示。

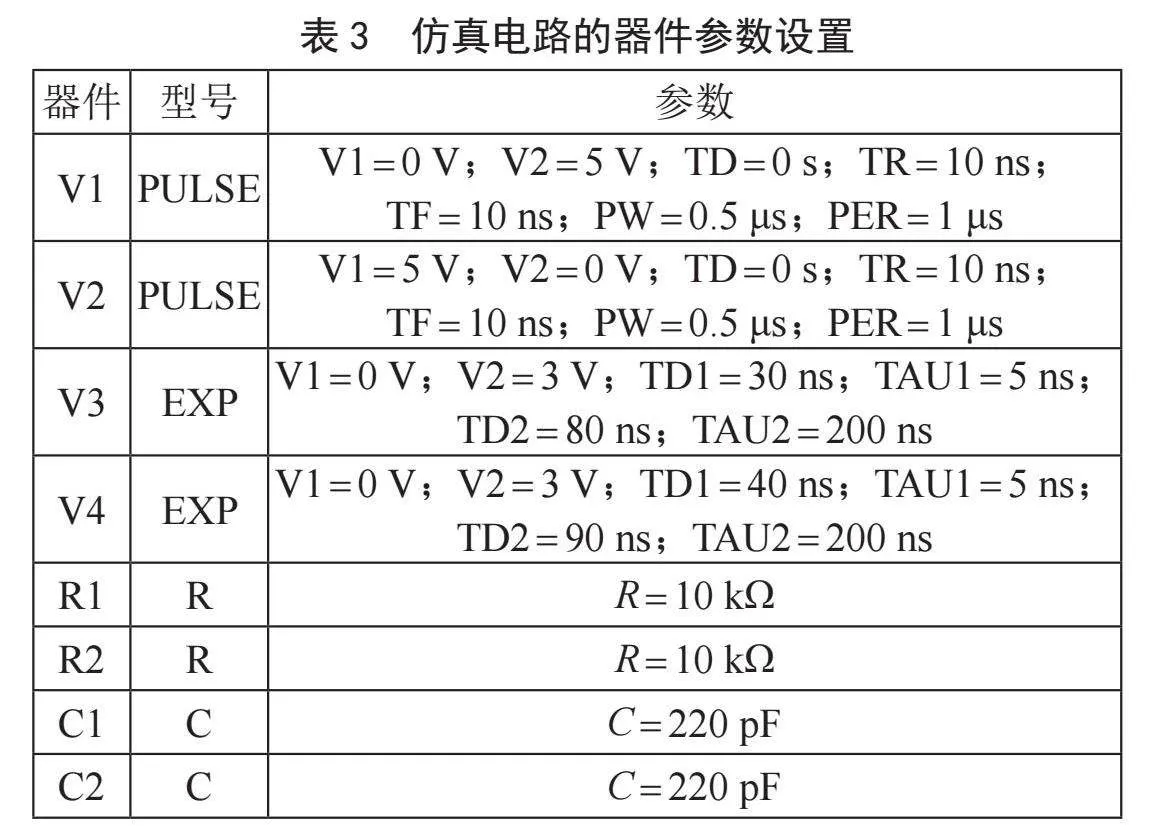

其中干扰源V3和V4分别代表共模干扰和差模干扰,采用双指数脉冲(double-exponential pulse)模型,上升时间tr=5 ns,持续时间td=50 ns,幅值为3 V。信号源采用周期为1 μs、占空比50%的方波,模拟500 bit/s的通信速率。分压电阻R1/R2取10 kΩ,滤波电容C1/C2取220 pF,对应的截止频率约为72 kHz,如表3所示。

仿真结果表明,未经滤波的信号在脉冲干扰的作用下出现严重的毛刺和电平飞升,导致接收错误和误码。而经过RC滤波后的信号则受干扰影响大大降低,各二进制数字的高低电平均得以正确判决[6]。仿真得到的未滤波信号和滤波后信号的特征参数对比如表4所示。

由表4可见,RC滤波使信号的峰峰值、过冲量、上升/下降时间等指标均得到改善,且脉冲宽度变化不大,证明了所提出的自适应滤波技术能有效抑制纳秒级脉冲干扰,且不影响正常通信。

3" 抗干扰芯片的应用效果

3.1" 改进前后的眼图、波形对比

为评估抗干扰芯片的改进效果,对改进前后的差分接收器进行了眼图测试和波形观测。结果表明,改进前的接收器眼图严重闭合,信噪比低,抖动大,波形毛刺明显;采用自适应滤波技术改进后,眼图质量显著提高,开口率、信噪比和抖动等指标均得到改善,波形毛刺大大减小。证实了所提出的技术能有效改善差分接收器的抗干扰性能,保证数据传输的可靠性[7]。

3.2" 不同波特率下的抗干扰性能

为考察抗干扰芯片在不同通信速率下的性能表现,针对常见的RS485/CAN波特率,测试了改进前后差分接收器的抗干扰容限曲线,即误码率BER=10-9时的等效干扰幅度。

测试结果表明,采用自适应滤波技术后,差分接收器在各个波特率下的抗干扰容限均得到大幅提高,尤其是在中低速率(10 kbit/s)下,容限电平提高了911 dB,在较高速率下也有8 dB以上的改善。例如在500 kbit/s速率下,抗干扰容限从2.1 Vpp提高到6.8 Vpp,提高了10.2 dB。改进后的抗干扰芯片能够适应不同的通信速率要求,在较宽的波特率范围内表现出优异的抗干扰性能,大大增强了接口电路的适应性和可靠性。

3.3" 稳定性、可靠性提升

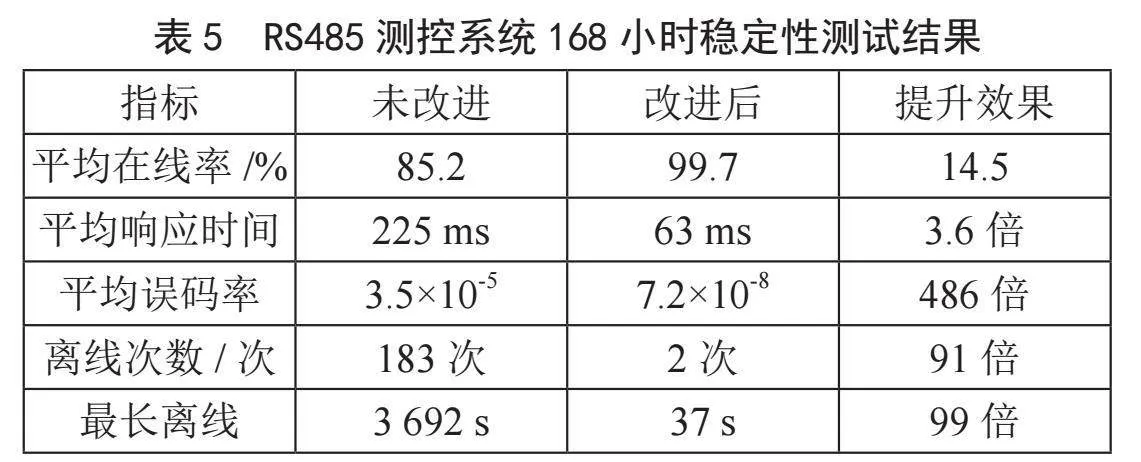

为评估抗干扰芯片在实际应用中的稳定性和可靠性,搭建了基于RS485总线的测控系统,包括1个主站和16个从站,采用菊花链型拓扑结构,总线电缆长度200 m。测试中分别使用改进前和改进后的RS485收发器芯片,在工频220 V供电环境下,观测各从站的在线率、响应时间、误码率等指标[8]。经过1周(168小时)的连续测试,结果如表5所示。

测试结果表明,采用抗干扰芯片改进后,RS485测控系统的稳定性和可靠性得到显著提升。从站的平均在线率由85.2%提高到99.7%以上,响应时间缩短了3.6倍,误码率降低了近500倍。整个测试期间,系统仅发生2次从站离线,累计离线时间不超过1分钟。与之相比,未改进的系统则出现了183次从站离线,平均每天超过1次,最长离线时间超过1小时。频繁的通信中断严重影响了系统的可用性和可靠性。

上述结果充分证明,自适应滤波技术能够极大地改善RS485总线系统的抗干扰能力,保障通信的长期稳定和可靠运行,从而提高系统的可用性和维护效率。

4" 芯片方案的应用前景

4.1" 在供配电、储能、充电桩等领域的应用价值

随着高速开关器件在供配电、储能、充电桩等领域的广泛应用,产生的电磁干扰日益严重,给RS485/CAN等通信接口带来巨大挑战。采用自适应滤波抗干扰芯片能有效抑制开关器件产生的高频脉冲干扰,确保通信高可靠、低误码,避免设备误动作或失控,在供配电自动化、微电网、储能变流器、充电机、电动汽车BMS等领域具有广阔应用前景。

以充电桩为例,内部变换器开关会在RS485/CAN总线上产生幅值高达数伏的纳秒级尖峰脉冲,常规接口电路难以可靠工作。采用抗干扰芯片后,即使在严重干扰下,通信可靠性得到有效保障,提高了设备可用性和安全性[9]。

在智能变电站和配电自动化系统中,大量设备通过总线互联,受开关设备、变压器等强电磁干扰影响,通信异常时有发生。采用抗干扰芯片可大幅减少通信误码和重发,提高系统实时性和可靠性。

4.2" 推广应用的建议

鉴于自适应滤波抗干扰芯片在提高通信可靠性方面的突出优势,建议从以下几个方面推动其推广应用。加强与芯片制造商合作,推动芯片产业化生产和规模化应用,降低成本,满足市场需求。在相关行业标准中增加抗干扰性能考核指标,引导设备制造商采用高可靠接口芯片,提高电磁兼容性。加大技术宣传和推广力度,让更多厂商和用户认识到芯片的优势和价值,加速推广进程[10]。

针对具体行业和设备特点,开发满足不同需求的芯片型号和参数规格,提供全面解决方案。密切跟踪电力电子技术进展,持续改进芯片抗干扰性能,保持技术先进性和实用性。加快抗干扰芯片推广应用,对提高电力电子设备可靠性和电能质量水平具有重要意义。

5" 结" 论

本文提出的自适应滤波技术串行通信收发器抗干扰芯片,通过在芯片内部引出RC滤波端口的微小改动,即可显著提升抗干扰性能,具有设计简单、改动小、应用范围广的特点。该方案有望成为RS485/CAN等串行总线在高干扰环境下的一种通用解决方案,对于提高相关领域设备的可靠性和稳定性具有重要意义。下一步应加快该技术的工程化应用,并推动行业标准的完善,以更好地满足电力电子设备发展的需求。

参考文献:

[1] 陈伟,蒲红平,杨仕勇,等.基于奈奎斯特采样的FPGA异步串行通信接口设计 [J].现代信息科技,2024,8(9):24-28+33.

[2] 陈硕,李梓欣,晋玉婷,等.高性能串行接口控制器的设计 [J].集成电路应用,2023,40(12):28-29.

[3] 陈谦,马迅.波特率自适应串行通信方法研究 [J].中国集成电路,2019,28(4):61-65.

[4] 王晓莉.高速串行系统建模及自适应模拟均衡器的设计 [D].南京:东南大学,2016.

[5] 徐胜,文丰.基于FPGA的UART自适应接收IP核设计 [J].单片机与嵌入式系统应用,2023,23(11):14-16+20.

[6] 李瑞.基于FPGA的串行通信MD5加密算法的研究与实现 [D].哈尔滨:哈尔滨理工大学,2019.

[7] 侯佩儒,曹炳尧,宋英雄.基于模拟串行端口的虚拟设备通信技术研究 [J].计算机测量与控制,2023,31(10):255-262.

[8] 姚莉,顾煜新.异步串行通信接口位置特征自动匹配优化方法 [J].计算机仿真,2022,39(3):215-219.

[9] 冯希昆.面向RS485串行通信接口芯片的静电浪涌防护设计 [D].无锡:江南大学,2022.

[10] 吴桐.高速串行通信信号抖动关键技术的研究 [D].合肥:中国科学技术大学,2023.

作者简介:张树宏(1969.02—),男,汉族,甘肃庆阳人,仪器仪表技术高级工程师,本科,研究方向:电力仪器仪表、新能源技术开发及测试。