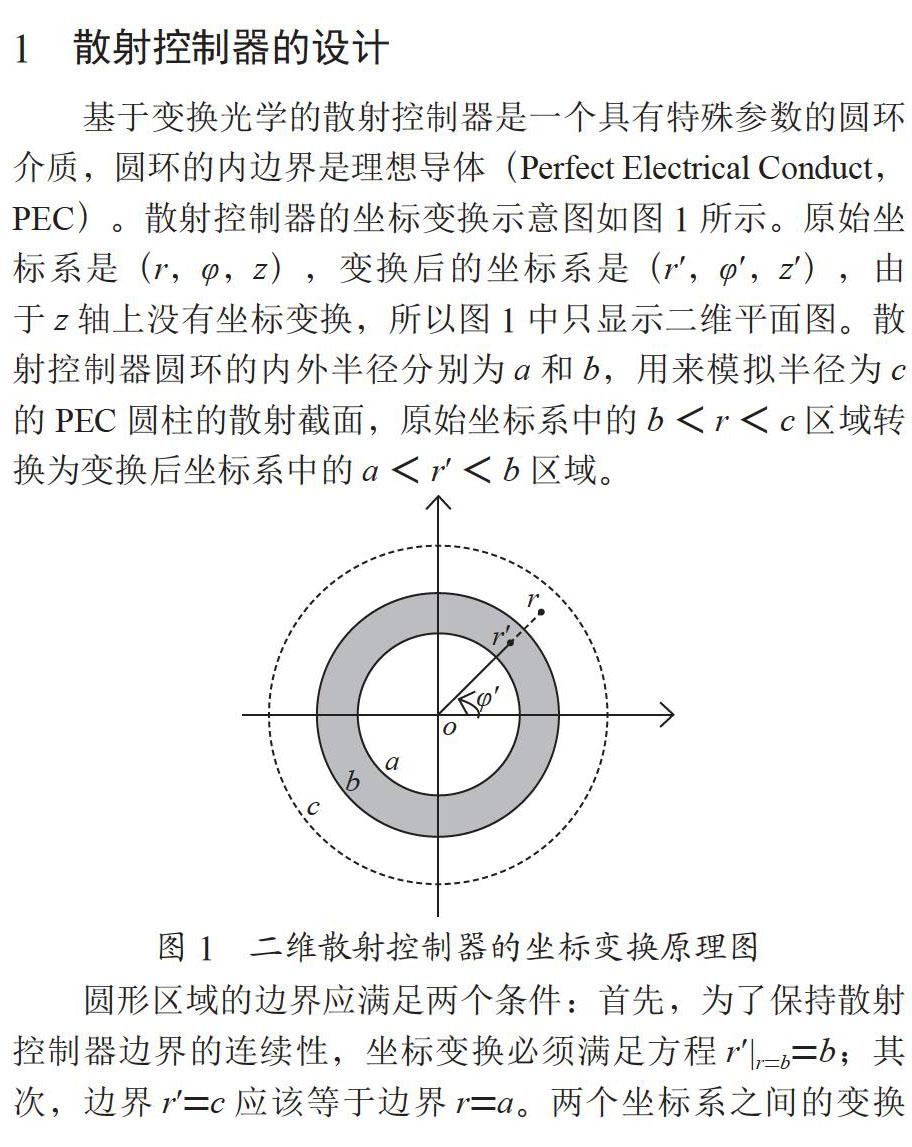

摘" 要:文章提出一种基于DMA多通道的数据传输机制,用以提高PC机、运动控制器,以及伺服驱动器间的数据传输效率和精度。文章首先给出一种基于“FPGA+DSP”架构的运动控制器设计方法。这种设计方法通过在DSP内部构建多组DMA通道,从而实现运动控制器与伺服驱动器之间的数据高速传输。同时,利用FPGA搭建出PC机与运动控制器间的DMA通道。接着通过DSP与FPGA之间协同工作策略,从而实现了PC机、运动控制器、伺服驱动器之间的数据高速传输。对比传统利用I/O通道进行数据交互的方法,文章提出的DMA多通道的数据传输机制具有传输效率高、波动性率小,以及实时性强的优点。

关键词:运动控制系统;DSP;FPGA;DMA多通道数据传输;实时性

中图分类号:TP332" 文献标识码:A" 文章编号:2096-4706(2024)23-0184-05

Research on Multi-channel DMA Transmission Mechanism Based on Motion Control System

LI Mingyang

(JAKA Robotics Co., Ltd., Shanghai" 200241, China)

Abstract: This paper proposes a data transmission mechanism based on multi-channel DMA to improve the efficiency and accuracy of data transmission among PC machine, motion controller and servo driver. This paper gives a motion controller design method based on “FPGA+DSP” architecture. This design method realizes high-speed data transmission between the motion controller and the servo driver by building multiple groups of DMA channels inside the DSP. At the same time, the DMA channel between PC machine and the motion controller is built by using FPGA. Then, the cooperative working strategy between DSP and FPGA realizes the high-speed data transmission among PC machine, motion controller and servo driver. Compared with the traditional method of using I/O channel for data interaction, the data transmission mechanism of multi-channel DMA proposed in this paper has the advantages of high transmission efficiency, low volatility rate, and strong real-time performance.

Keywords: motion control system; DSP; FPGA; DMA multi-channel data transmission; real-time performance

0" 引" 言

以PC机为基础的运动控制系统由PC机与运动控制器组成。PC机负责路径规划,并将生成的粗插补点传输给运动控制器。运动控制器则完成闭环计算并实时控制电机[1]。系统运行涉及大量的数据处理,需管理PC与运动控制器间的数据传输,以及运动控制器内部芯片的数据传输。

PC与运动控制器间的数据传输有两种形式。一是由PC机主导数据传输。但实时性难以保证,即使使用Vxworks,最小时间片也仅为10 ms[2]。另一种是运动控制器主导数据传输。通过PCI、光纤、实时以太网、工业现场总线等总线与PC机相连。并通过共享内存同步数据,可达微秒级控制。因此总线选择直接影响传输效率。如CAN总线的传输速率为0.125 MB/s[4]。虽然它利用串行通信的方式可实现多台设备间的实时通信。但CAN总线传输速率易受到距离的影响。当传输距离大于10 km时,它的传输速率就会降到0.625 kB/s。再比如工业以太网,它具有传输速率高网络分布性强的优点。但因为以太网协议一直没有统一的标准,所以不易在FPGA中实现[5]。目前常用的PCI总线普遍采用I/O通道进行传输 (即单个数据传输),这种传输方式具有33 MB/s的传输速率,如果采用DMA通道进行传输时 (即批量数据传输),其速度可达到132 MB/s[6]。但是这种DMA传输方式目前普遍应用在数据采集领域[7],在运动控制领域中少有研究。可以预见的是,如果运动控制器和PC机间采用基于PCI总线的DMA数据传输方式,其传输效率可得到大幅度的提升。因此,如何在运动控制器中构建PCI桥芯片以实现DMA数据传输,是本文的研究点之一。

在运动控制器内部普遍采用“总线协议芯片+FPGA+DSP”架构[8]。理论上传输峰值可达4个clock每字[9-10]。但在特定硬件环境下,实际传输效率仅为35.2 MB/s[11]。文献[12]中提到的DSP-Cache方法可以提高实际传输效率,但无法处理多组数据。因此如何实现多组数据DMA传输并避免冲突,这是本文另一个研究点。

鉴于此,本文提出了一种多通道DMA数据传输机制,实现PC与运动控制器及运动控制器内部的高速数据传输。设计“FPGA+DSP”架构的运动控制器,利用DSP多通道DMA管理器实现内部高速传输,将PCI协议和FIFO存储器嵌入FPGA中,建立PC与运动控制器间的DMA通道,由运动控制器主导数据传输,降低了对PC实时性的要求,提高了传输效率。

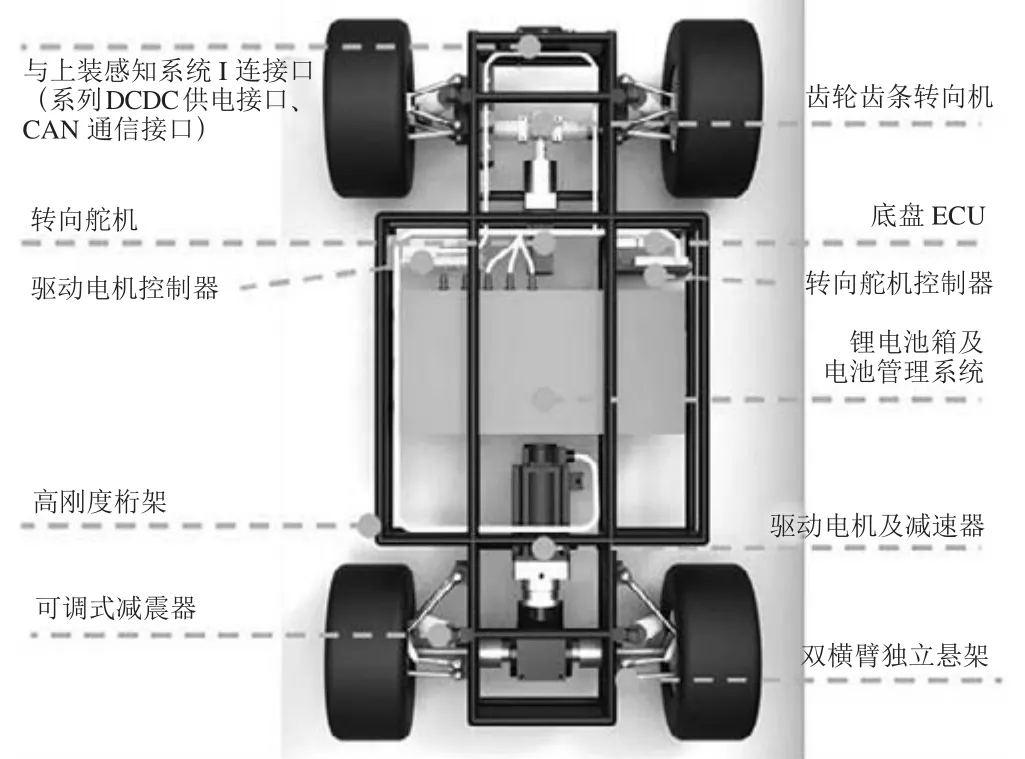

1" 系统框架

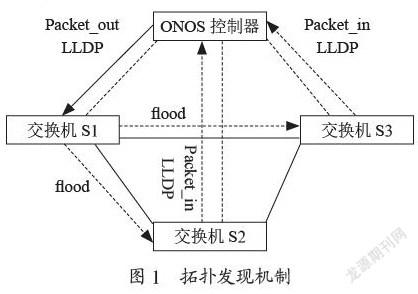

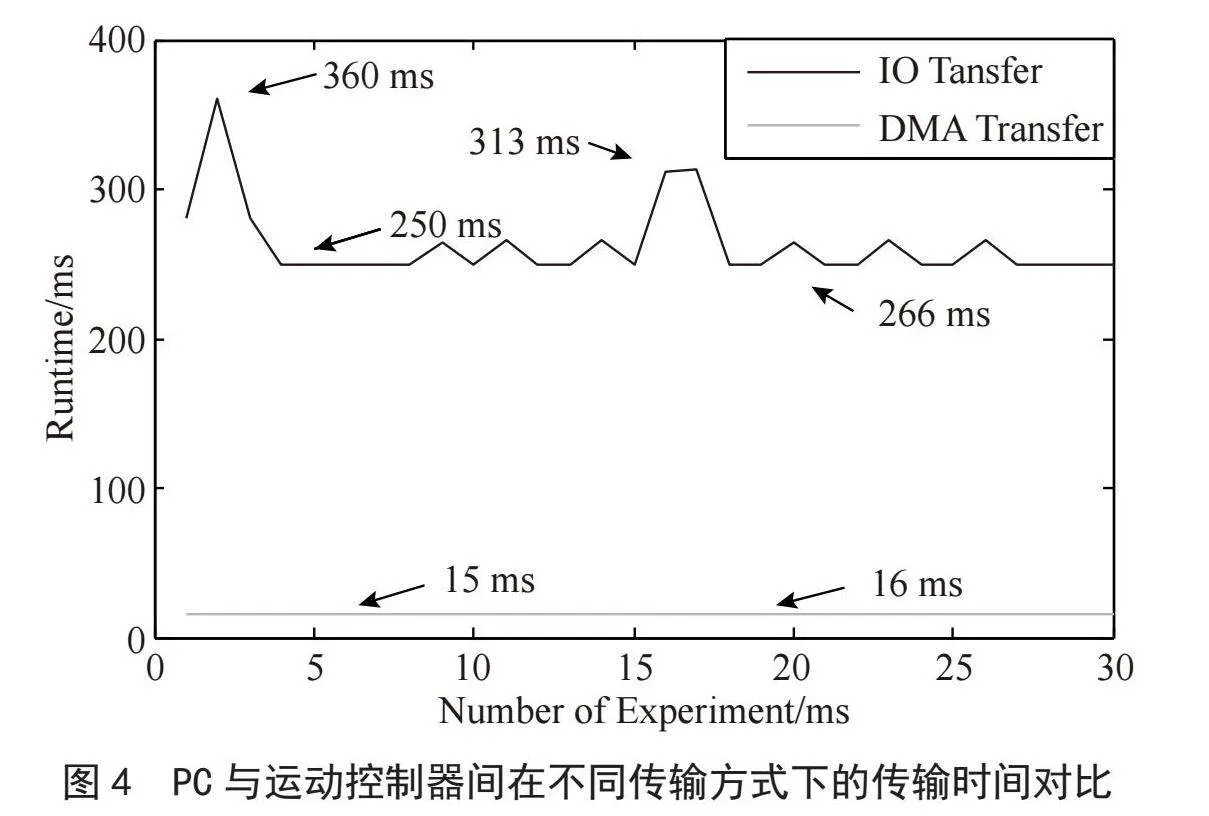

运动控制系统的数据传输框架如图1所示,由PC机、FPGA、DSP、伺服驱动模块组成。通过在FPGA中嵌入PCI协议,实现PC机与运动控制器之间的I/O与DMA数据传输。I/O传输少量命令与参数,DMA传输插补点和位置数据。在FPGA内搭建数据缓冲池与应答器,以同步PC机与运动控制器数据。

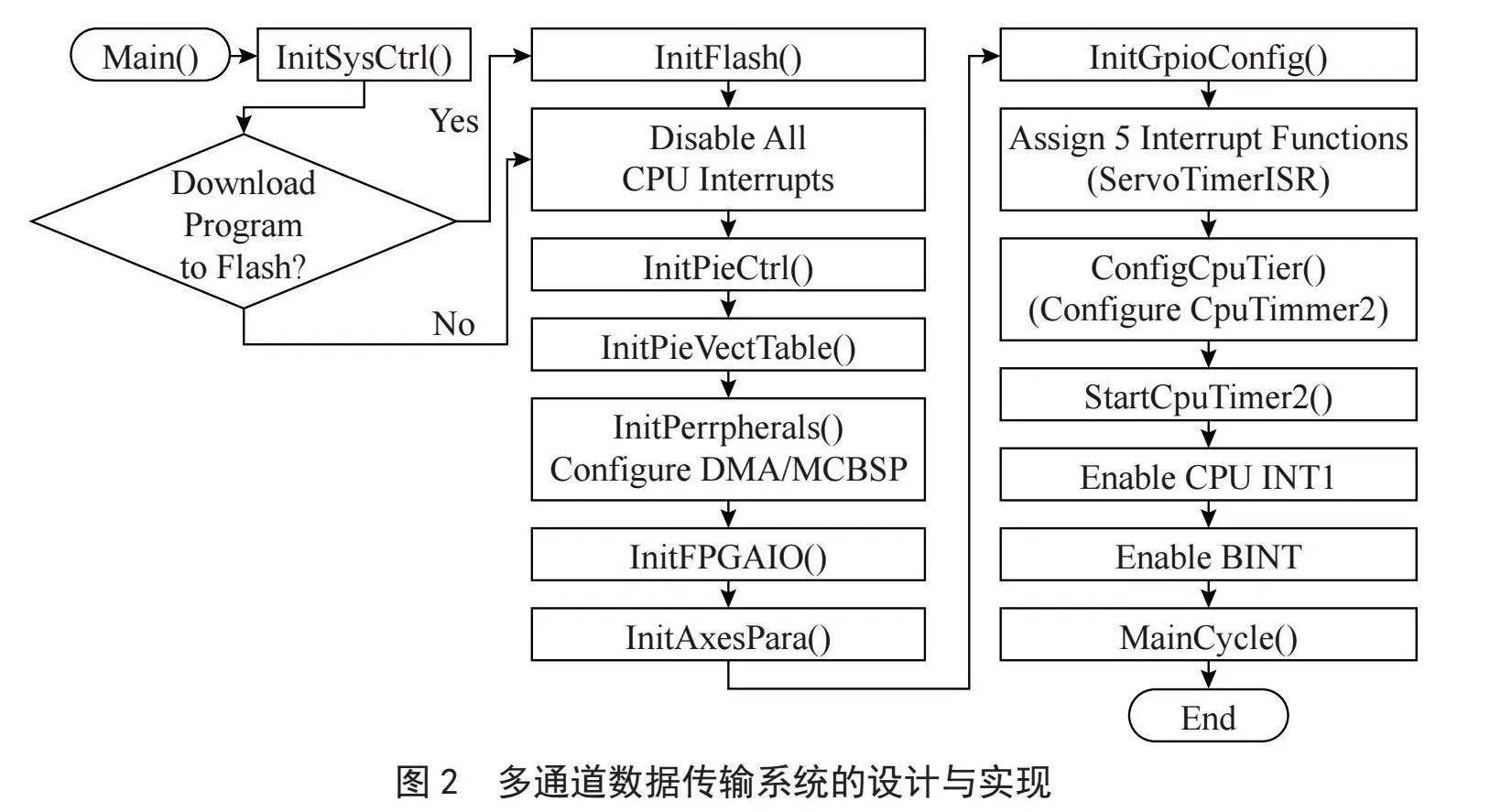

数据传输流程如图2所示:首先PC机通过DMA控制器将插补点数据包传FPGA,并存储于数据缓冲池中。随后,DSP利用DMA控制器从FPGA搬运数据至RAM,生成电机位置参考点。每个伺服周期,DSP从点集中提取位置参考点,与电机的实际位置进行闭环比对,结果传输至伺服驱动单元以实现电机运动。同时,实际位置数据传回PC机,完成数据流通。

2" 多通道数据传输系统的设计与实现

本文设计了一款基于“DSP+FPGA”构架的四轴运动控制器,以实现多通道数据传输。DSP选用TI公司的TMS320F28335芯片,它具有150 MHz的处理能力、32位浮点运算功能,并支持DA、MCBSP、EPWM、XINTF和SRAM口的数据传输接口。FPGA采用ALTERA公司的Cyclone 2系列芯片,其具有8 256个LE逻辑单元、125个I/O管脚、36个M4K存储空间、167M的I/O频率。除此之外,两块AD1866芯片负责将闭环计算的结果进行数模(DA)转换。将结果送至伺服驱动模块以实现电机控制。接下来,我们将详细介绍系统各模块。

2.1" DSP模块的设计与配置

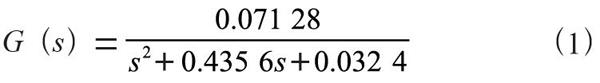

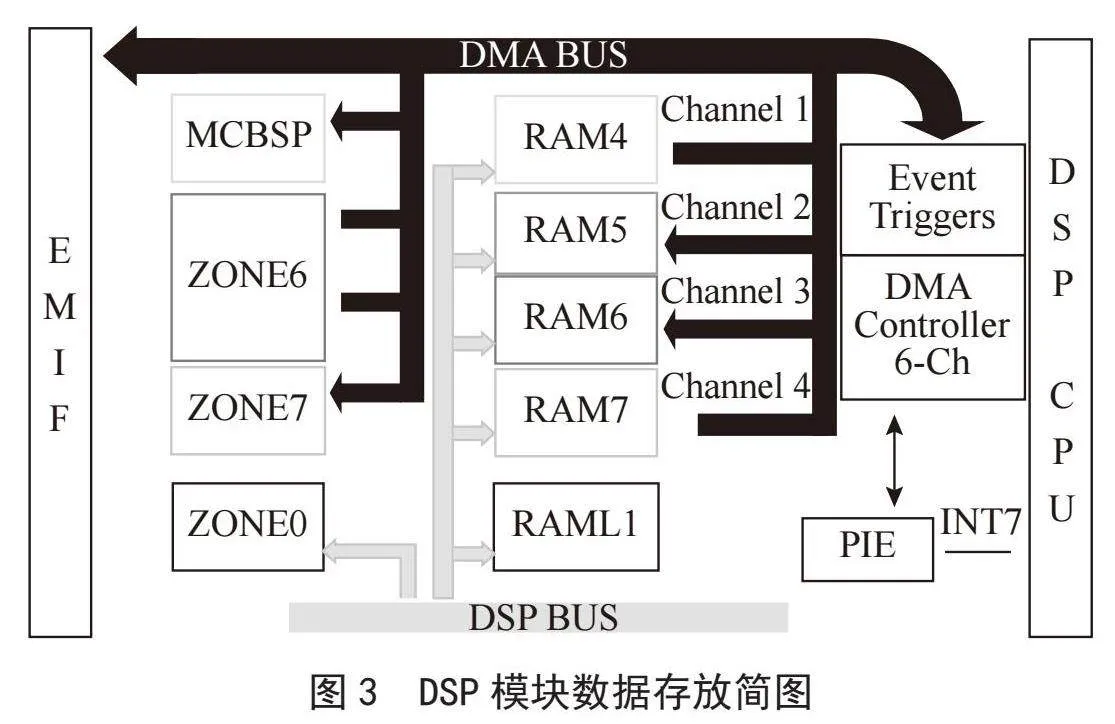

图3给出了DSP模块简图。由图可知,DSP通过External Memory Interface (EMIF)和Multichannel Buffered Serial Port (MCBSP)与FPGA进行数据连接。同时DSP通过XCLKOUT口与FPGA进行150 MHz的时钟同步。

DSP内部包括6个DMA通道和两条总线 (DMA总线和DSP总线)。传输速率配置如下:为保证DSP与FPGA之间达到37.5 MB/s的数据吞吐量,每隔8个CLOCK传输一个16位数据通过EMIF口。同时考虑到AD1866的最大传输速度,每256个CLOCK,DSP通过MCBSP口传输数据流给FPGA,再由FPGA内的COM-to-LPT模块转换并交给AD1866芯片,数据吞吐量为1.17 MB/s。也就是说,每个伺服周期中,RAM4空间前4个地址存储的4个轴的电机控制量都会通过DMA传输给AD1866芯片。

RAM5和RAM6各存放4 096个32位数据,与ZONE6挂接,用于保存PC机传输的两组插补点数据包。每隔40个伺服周期,DSP逐次从这两组内存中取出四个轴的粗插补点,并密化成40个精插补点,用于接下来的40个伺服周期的闭环计算,计算结果传输至AD1866芯片,实现电机运动。同时,光电编码器捕获四个轴的实际位置,数据保存在RAM7(2 048个32位数据)。RAM7与ZONE7相连。当RAM7满后,通过DSP和PCI的DMA总线传输至PC机。为避免数据交互期间总线冲突,将不同数据分配不同DMA传输通道,并通过PIE仲裁器分配传输时间片。

表1为DMA传输通道的设定值。在每个伺服周期,RAM4通过MCBSP口将闭环计算结果传输给FPGA控制电机运动。所以该数据放在优先级最高的DMA通道1中传输,而PC机和运动控制器之间需要传输的三个数据包,依次放入另外三个具有相同优先级的DMA通道中传输,数据包间采用“通道2→通道3→通道4→通道2……”的Round-robin方式进行传输。传输开始时,事件触发器会接收到传输请求后交由PIE仲裁,PIE将结果通知CPU。最后由DMA控制器完成数据迁移。如DMA通道1需要使用DMA总线,DMA控制器将完成当前BURST段传输并挂起,优先处理通道1数据。通道1传输结束后,继续先前未完成的传输。通过此方式保证运动控制系统对电机的实时控制。

DSP的程序采用C语言编写,并存储在RAML1中。程序由中断响应函数和通信函数组成。中断响应函数负责闭环计算、数据交互、参数更新及传输电机控制量。通信函数负责运动控制器与PC机间的命令与参数交互。利用中断的方式分配时间片,避免程序间的冲突。

2.2" FPGA模块设计与配置

FPGA模块负责连接PC机、DSP模块及伺服驱动模块。其内部包括PCI协议模块、数据缓冲池模块、应答机、COM-to-LPT模块和分频鉴相模块。PCI协议模块将运动控制器映射在PC内存中,实现运动控制器与PC机之间的通信;数据缓冲池模块由DAM缓冲池和I/O缓冲池组成,分别保存PC与DSP之间的批量数据及命令参数数据;应答机负责通知PC和DSP分时段访问缓冲池;COM-to-LPT模块将闭环计算的串行数据解析成各个轴的驱动信号;分频鉴相模块负责对光电编码器的信号进行滤波、倍频、鉴相处理捕获Z信号。

DMA缓冲池由两块FIFO组成,其利用QuartusⅡ软件中的MegaWizard Plug-in Manager (IP核)来构建。它的大小为8 192字节。在FIFO 0中保存了PC向运动控制器发送的粗插补点数据,FIFO 1保存了运动控制器向PC发送的实际位置点数据。DMA缓冲池两端分别挂载DSP译码模块和PCI协议模块。DSP译码模块将其他模块通过XINTF口映射到DSP的RAM中,使得DSP可以直接访问其他模块。PCI协议模块利用VHDL语言,基于PCI 2.1标准进行编写,使运动控制器能够被PC机正确识别,从而分配地址并引导主从通信模式。

应答机制用于PC与运动控制器间的批量数据传输。PC将插补点数据装载至FIFO 0后,应答器0置标志位1,DSP通过地址映射查询标志位,并在标志位为1时利用DMA通道将数据读入RAM中。同样,实际位置点数据存满FIFO 1后,应答器0触发通知PC,通过PCI DMA通道将数据传至PC内存。

I/O数据缓冲池由三个16位寄存器组成(寄存器0用于命令数据,寄存器1和2用于参数数据),由FPGA内置IP核建立。应答器1协调不同I/O通道的异步传输,PC发送命令和参数后,应答器1置1,DSP检测信号变化后取出数据处理并返回,PC接到通知后读取寄存器1和2的数据。

3" OM-to-LPT模块设计

在每个伺服周期,闭环运算得出的四个轴控制量会以串行数据流的形式发送给COM-to-LPT模块。每轴控制量为16位数据,因此数据流为64位。为保证传输的连续性,需要配置传输控制寄存器(XCR)、MCBSP位传输频率(CLKX)、帧频率(FPER),以及帧宽度(FWID)。在每个CLKX的上升沿,XCR会将数据流依次传输给数据发送引脚 (DX)。通过DMA 1通道以1.17 MB/s速率传输至COM-to-LPT模块。模块使用Verilog语言编写,根据FPER信号来产生4路片选信号。依据片选信号,AD1866芯片将数据流转换为四路电压信号,并交给伺服驱动单元完成电机运动。

4" 实验研究

4.1" 实验平台搭建

运动控制系统由一台工控机、一个四轴运动控制器,以及一组AC伺服驱动器组成。工控机采用研华610L的PC机,配置为E5300 2.6 GHz CPU、1 GB内存、250 GB硬盘,操作系统为WINDOWS XP SP3。运动控制器采用”DSP+FPGA”构架,其中DSP型号为TMS320F28335,FPAG为Cyclone 2。AC伺服驱动单元包含四组型号为SGDV-2R8A01A驱动器和四组SGMJV-04ADA21交流伺服电机。其最大转速为3 000转/分钟,转矩为1.27 N·m。

4.2" 实验结果及其分析

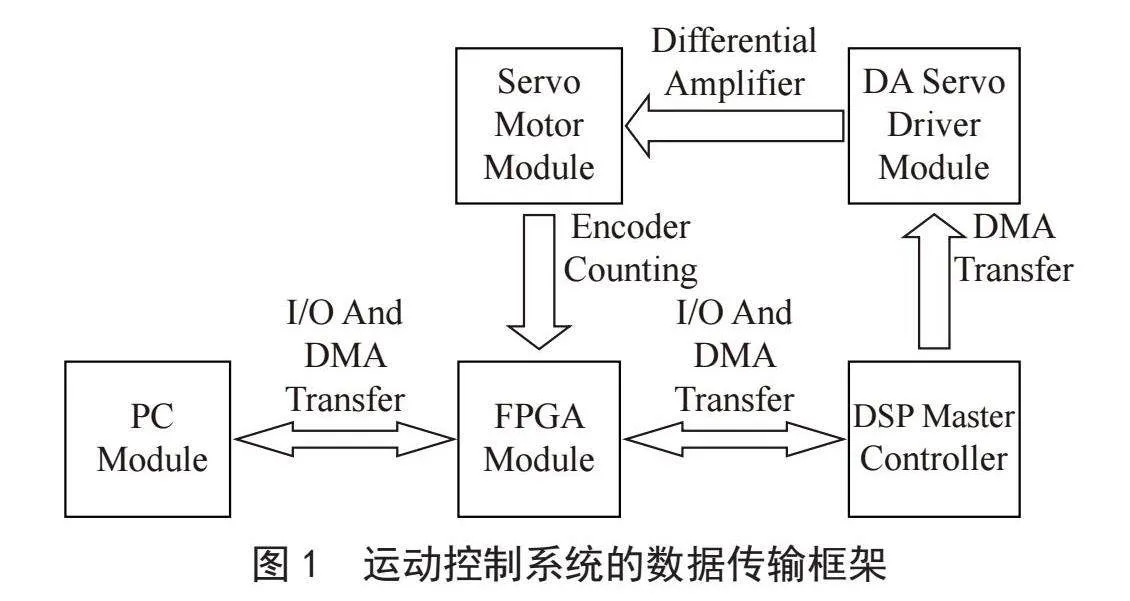

实验流程如下:PC机采用I/O和DMA方式访问运动控制器。首先PC机采用I/O方式传输2 048个32 bit插补点数据给运动控制器,再用DMA传输相同数量的数据。在数据传输过程中,PC机记录传输时间。运动控制器接收数据并处理生成四组新数据,通过不同的DMA通道传输,传输时间由DSP计时器记录。实验参数设置如下:数据包大小为2 048个32位数据;PCI传输速率为132 MB/s,32位总线宽度;DSP总线宽度为16位,DSP的XINTF选用Zone6和Zone7口,读写速率为37.5 MB/s;MCBSP口CLKG频率为16个cycles,帧同步周期为256个cycles,传输长度为16位。实验重复30次。

图4给出PC机与运动控制器间数据传输时间。蓝色实线表示采用I/O方式传输2 048个32 bit数据的时间。红色虚线为DMA方式传输相同数据的时间。实验结果显示,I/O方式传输时间在250 ms到360 ms之间波动,均方差(MSE)为24.6 ms。而DMA方式平均耗时为15.6 ms,MSE为0.48 ms。对比可知,DMA方式可将传输速率较I/O方式提高了16倍,均方差降低了98%。

通过四组运动控制器内部的数据传输时间可知,这四组数据在四个DMA通道中的传输速度基本相同,为6.826 μs、218.453 μs、218.453 μs和218.453 μs。本文采用DSP主导数据传输,并与FPGA共享时钟频率以确保时钟同步,从而有效提升数据传输的稳定性。此外,DMA传输无须CPU干预,从而降低运动控制器的计算负荷,有效提高数据传输的效率。

5" 结" 论

本文提出一种基于DMA多通道的数据传输机制。文章首先架构了PC机与运动控制器间的DMA通道,然后在运动控制器内部构建了多个DMA通道。通过PC机与运动控制器协作的方式,实现数据在PC机、运动控制器,以及伺服驱动模块之间稳定高效地传输。文章最后进行了数据传输实验,结果表明本文提出的传输方法具有硬件结构简单、传输波动性小,以及实时性强的优点。

参考文献:

[1] YEH S S,HSU P L. Analysis and Design of Integrated Control for Multi-axis Motion Systems [J].IEEE Transactions on Control Systems Technology,2003,11(3):375-382.

[2] BARBALACE A,LUCHETTA A,MANDUCHI G. Performance Comparison of VxWorks,Linux,RTAI and Xenomai in a Hard Real-time Application [J].IEEE Transactions on Nuclear Science,2008,55(1):435-439.

[3] DOZIO L,MANTEGAZZA P. Linux Real Time Application Interface (RTAI) in Low Cost High Performance Motion Control [J].Motion Control,2003:27-28.

[4] HSIEH C C,HSU P L. The CAN-based Synchronized Structure for Multi-axis Motion Control Systems [J].IEEE International Conference on Systems,2005 (2) 1314-1319.

[5] JUNG I K,LIM S. An EtherCAT based Control System for Human-robot Cooperation [C]//16th International Conference on Methods and Models in Automation and Robotics. Miedzyzdroje:IEEE,2011:341-344.

[6] BUREŠ P. The Problems of Continuous Data Transfer between the PC User Interface and the PCI Card Control System [M]//Jabloński R,Březina T. Mechatronics,Berlin:Springer,2012:483-487.

[7] YAN J,WU N. High Speed DMA Data Transfer System Based on PCI Bus [J].Journal University of Electronic Science and Technology of China,2007,36(5):858-861.

[8] HUANG F Q,LIN W P. Design of Laser Processing System of Five-Axis Motion Controller Based on DSP and FPGA [J].Advanced Materials Research,2014,846:98-102.

[9] YOLACAN E,AYDIN S,ERTUNC H M. Real time DSP based PID and State Feedback Control of a Brushed DC Motor [C]//International Symposium on Information,Communication and Automation Technologies.Sarajevo:IEEE,2011:1-6.

[10] TI Instruments. TMS320x2823x Technical Reference Manual [EB/OL].[2024-07-27].https://www.ti.com.cn/cn/lit/ds/symlink/tms320f28335.pdf?ts=1733357922951

[11] JIA Q,HUANG Z,LIU Y. Study on Performance of PCI Interface for Embedded System [J].Future Communication Technology,2014,51(2):3-12

[12] 郭强,张斌.基于DMA的DSP-Cache优化 [J].电气电子教学学报,2009,31(2):50-53.

作者简介:李明洋(1981—),男,汉族,江苏淮安人,本科,研究方向:机器人感知与控制技术、机器人应用与开发、人机交互技术。